Table Of ContentSistemas de Adquisición de Datos

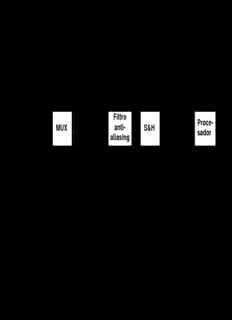

Sistema de adquisición de datos

Circuito de

Selección de muestreo y

las señales

retención

programable

Sensores Filtro

Proce-

MUX AMP anti- S&H ADC

sador

aliasing

Amplificador Convertidor

de ganancia analógico-

programable digital

La señal entregada por los sensores suele ser débil.

El amplificador puede ser diferencial, y con aislamiento galvánico.

Se puede añadir el camino opuesto formado por un DAC y un filtro de

reconstrucción para obtener un sistema bidireccional.

1

Sistemas de Adquisición de Datos

Sistema de control

El procesador o controlador recibe información del estado del sistema, y

actúa en consecuencia.

Convertidor

Transductor de

analógico-

presión

Electroválvula digital

AMP

MUX S&H ADC

AMP Proce-

sador

Convertidor

Termopar digital-

analógico

Calentador

Actuador DAC

Red de

Actuador

comunicación

2

Sistemas de Adquisición de Datos

Amplificador con aislamiento galvánico

El aislamiento galvánico protege al sistema de adquisición de las tensiones

elevadas que podría haber en los puntos de medida. También sirve para

reducir el ruido en modo común.

Aislamientog

alvánico

Amplificador Amplificador

1 2

Métodos de acoplo empleados para obtener el paso de la señal sin conexión

eléctrica directa:

Acoplamiento inductivo (mediante transformador)

Acoplamiento capacitivo (mediante condensador)

Acoplamiento óptico (mediante IRLED y fotodiodo)

Cada amplificador (1 y 2) debe tener su propia masa y su alimentación (aisladas

entre sí)

3

Sistemas de Adquisición de Datos

Ejemplo de aislamiento óptico

El IRED y los dos fotodiodos (FD1 y FD2)) forman parte de un único

encapsulado. El proceso de fabricación garantiza que la relación entre la

cantidad de luz que reciben FD1 y FD2 es prácticamente la misma para

cualquier corriente en el IRED dentro de un rango (diferencia < 0,1 %).

Sin embargo, la relación entre la corriente aplicada al IRED y la que se

genera en los fotodiodos es claramente alineal.

El circuito garantiza una

buena linealidad.

Ii = corriente inversa en FD1

If = corriente inversa en FD2

Vi = Ii * Ri.

Vo = If * RF

If / Ii = k (cte.)

Entonces, Vo / Vi = k*RF/Ri

4

Sistemas de Adquisición de Datos

Interruptores analógicos

Los interruptores analógicos son dispositivos con dos estados que permiten cerrar y

abrir un circuito eléctrico, facilitando de esta forma el control de paso de una señal. El

estado se define mediante una tensión de control. Idealmente, la resistencia en el

estado de conducción debería ser 0, y en el estado de no conducción debería ser

infinita. Estos dispositivos son útiles para el diseño de circuitos de muestreo y

retención (S&H), convertidores DAC y ADC, y en otras aplicaciones.

Los relés (relevadores electromagnéticos) se pueden utilizar como interruptores

analógicos. El tipo de relé más utilizado para esta aplicación es el rele reed, por su

pequeño tamaño y su moderado consumo de corriente de control. Sin embargo, su

tiempo de conmutación (tc) es elevado (> 1 ms), y pueden presentar rebotes.

Ω Ω

Ron < 0,1 Roff > 1 T

El relé reed está formado por una ampolla de vidrio rodeada por una bobina.

En el interior hay dos contactos metálicos (magnéticos) que se unen cuando

existe un campo magnético suficientemente intenso.

5

Sistemas de Adquisición de Datos

Puerta analógica CMOS

Los interruptores analógicos basados en semiconductores son los más utilizados. El

interruptor más común es la puerta analógica CMOS.

Ω Ω

Ron=10 a 300 . Roff=100 M . tc= 200 ns.

M1 y M2 forman un inversor.

Con la señal de control Vc a nivel alto, el canal de M4

(MOS de canal N) presenta una resistencia baja (300

ohm typ).

Con Vc alto, la salida del inversor está a nivel bajo, el

nivel necesario para que conduzca M3 (MOS de canal

P).

Con Vc a nivel bajo, no conduce ninguno de los

transistores que forman el interruptor (M3, M4)

http://www.csee.wvu.edu/~digital/book/chapters/advcmos.pdf

6

Sistemas de Adquisición de Datos

Multiplexor/demultiplexor (analógico)

El multiplexor analógico está Selección de MDX

entrada (n bits)

formado por un decodificador y un

conjunto de puertas analógicas.

El multiplexor analógico es

Salida

reversible, es decir, se pueden

analógica

n

2 entradas

usar las entradas como salidas, y

analógicas

la salida como entrada.

La entrada seleccionada queda

conectada eléctricamente a la salida

a través de una resistencia de bajo valor.

En las familias CMOS de circuitos integrados digitales (4000, 74HC, 74HCT) se

encuentran varios tipos de puertas y multiplexores analógicos, que incluyen

entradas auxiliares como la de inhibición (INH).

http://www.analog.com/en/switchesmultiplexers/multiplexers-muxes/ad8182/products/product.html

7

Sistemas de Adquisición de Datos

Circuitos de muestreo y retención (S&H)

Los circuitos de muestreo y retención (Sample & Hold) se utilizan para

obtener muestras de señales analógicas (generalmente muestras de tensión).

Poseen dos estados de funcionamiento:

1) Estado de muestreo o seguimiento (sample). La salida sigue a la entrada.

2) Estado de retención (hold). La salida retiene el valor que tenía la entrada en el

momento del cambio a este estado.

Los circuitos de S&H utilizan un condensador para retener o memorizar las

muestras de tensión. El circuito básico se muestra en la figura.

Ri

v v

i o

I

Ron C RL

Roff

Coff

8

Sistemas de Adquisición de Datos

Aplicaciones del circuito S&H:

Su principal aplicación se encuentra en los sistemas de adquisición de

datos, como circuito previo al convertidor analógico digital. Los convertidores

de aproximaciones sucesivas requieren el uso de un circuito de S&H para evitar

que el valor que se está determinando pueda cambiar antes de finalizar la

medida. Como excepción, los convertidores de aproximaciones sucesivas

basados en conmutación de condensadores (por ejemplo TLC1543 de Texas) no

requieren circuito de S&H, ya que los condensadores empleados para la

conversión realizan implícitamente la tarea de muestreo y retención.

Es importante advertir que otros tipos de convertidores no requieren el

empleo de un S&H. Los convertidores de tipo integrador (como el de doble

rampa) pueden operar sin S&H, en cuyo caso miden el valor medio de la señal

durante el ciclo de integración. Si utilizan un circuito de S&H, la medida se

realiza sobre el valor instantáneo retenido.

9

Sistemas de Adquisición de Datos

Durante la fase de muestreo el interruptor I se mantiene cerrado. Durante la

fase de retención se mantiene abierto. El interruptor es electrónico y se puede

realizar mediante transistores bipolares, JFET o MOS. Su resistencia Ron

ΩΩΩΩ

debería ser idealmente cero, pero suele ser de decenas o centenas de . Su

ΩΩΩΩ

resistencia Roff debería ser infinita y suele ser superior a 1 G en la práctica.

Idealmente, Ri debería ser 0 y RL infinita. Además, la señal digital de control

empleada para abrir y cerrar el interruptor se transmite en cierta medida a la

salida, debido a la existencia de capacidades parásitas (crosstalk).

A continuación se definen algunos términos empleados con frecuencia en el estudio de los circuitos de S&H.

Tiempo de adquisición (acquisition time).- El tiempo necesario para que la salida del S&H actualice su valor al de una

nueva muestra, con un error determinado. Se especifica para un determinado salto de tensión (cambio con relación a la

muetra anterior), por ejemplo 5V. El error se especifica generalmente como un porcentaje del salto (por ejemplo 0,1 %). Se

puede interpretar como el tiempo que se debe mantener el interruptor cerrado para lograr la carga del condensador (Ri, Ron

distintas de cero). Otro efecto a tener en cuenta es la inductancia parásita del condensador, que no es despreciable si se

emplea un condensador electrolítico. Este tiempo se puede ver incrementado por el uso de un operacional lento (ver

apartado 2). Este tiempo es mayor si se utilizan condensadores con mayor capacidad.

Tiempo de apertura (aperture time).- El tiempo mínimo que debe transcurrir desde la orden de retención (hold) para que los

posteriores cambios en la entrada no afecten a la salida. Se puede interpretar como el tiempo que el interruptor tarda en

abrirse.

Error dinámico de muestreo (dynamic sampling error).- Error que aparece en la salida como resultado de que la entrada

esté variando en el momento de la orden de retención (hold). Se suele expresar en mV, para una determinada pendiente de

cambio (slew rate) de la entrada. Este error está presente aunque los tiempos de muestreo sean muy grandes, ya que se

debe al retardo introducido por la constante de tiempo (Ri+Ron)·C, despreciando RL.

10

Description:interruptor más común es la puerta analógica CMOS. Ron=10 a 300 Ω. Roff=100 MΩ. tc= 200 ns. M1 y M2 forman un inversor. Con la señal de control