Table Of ContentADS6445-EP

ADS6444-EP

www.ti.com SLAS573C–FEBRUARY2008–REVISEDMAY2013

QUAD CHANNEL, 14 BIT, 125/105 MSPS ADC WITH SERIAL LVDS OUTPUTS

CheckforSamples:ADS6445-EP,ADS6444-EP

FEATURES APPLICATIONS

1

• MaximumSampleRate:125MSPS • Base-StationIFReceivers

• 14-BitResolutionwithNoMissingCodes • DiversityReceivers

• SimultaneousSampleand Hold • Medical Imaging

• 3.5-dBCoarseGainand upto6-dB • TestEquipment

ProgrammableFineGainfor SFDR/SNRTrade-

Off SUPPORTS DEFENSE, AEROSPACE,

AND MEDICAL APPLICATIONS

• SerializedLVDS OutputswithProgrammable

InternalTerminationOption • ControlledBaseline

• SupportsSine,LVCMOS,LVPECL,LVDSClock • OneAssemblyandTestSite

InputsandAmplitudeDownto400mV

PP • OneFabricationSite

• InternalReferencewithExternalReference

• AvailableinMilitary(–55°Cto125°C)

Support

TemperatureRange

• NoExternalDecouplingRequiredfor

• ExtendedProductLifeCycle

References

• ExtendedProduct-ChangeNotification

• 3.3-VAnalogand DigitalSupply

• ProductTraceability

• 64-pinQFNPackage(9mm×9mm)

• FeatureCompatibleDual ChannelFamily Table1.ADS644XQuadChannelFamily(1)

125MSPS 105MSPS

ADS644X

ADS6445 ADS6444

14Bit

(1) ProductPreviewforADS6444

Table2.PerformanceSummary

ADS6445 ADS6444

Fin=10MHz(0dBgain) 87 91

SFDR,dBc

Fin=170MHz(3.5dBgain) 79 83

Fin=10MHz(0dBgain) 73.4 73.4

SINAD,dBFS

Fin=170MHz(3.5dBgain) 68.3 69.3

Power,perchannel,mW 420 340

DESCRIPTION

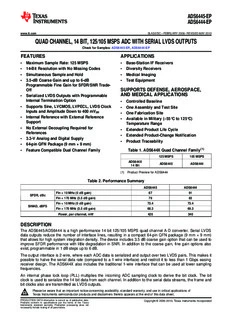

The ADS6445/ADS6444 is a high performance 14 bit 125/105 MSPS quad channel A-D converter. Serial LVDS

data outputs reduce the number of interface lines, resulting in a compact 64-pin QFN package (9 mm × 9 mm)

thatallowsforhighsystemintegrationdensity.Thedeviceincludes3.5dBcoarsegainoptionthat canbeusedto

improve SFDR performance with little degradation in SNR. In addition to the coarse gain, fine gain options also

exist,programmablein1dBstepsupto6dB.

The output interface is 2-wire, where each ADC data is serialized and output over two LVDS pairs. This makes it

possible to halve the serial data rate (compared to a 1-wire interface) and restrict it to less than 1 Gbps easing

receiver design. The ADS644X also includes the traditional 1-wire interface that can be used at lower sampling

frequencies.

An internal phase lock loop (PLL) multiplies the incoming ADC sampling clock to derive the bit clock. The bit

clock is used to serialize the 14 bit data from each channel. In addition to the serial data streams, the frame and

bitclocksalsoaretransmittedasLVDS outputs.

1

Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsof

TexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet.

PRODUCTIONDATAinformationiscurrentasofpublicationdate. Copyright©2008–2013,TexasInstrumentsIncorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarilyincludetestingofallparameters.

ADS6445-EP

ADS6444-EP

SLAS573C–FEBRUARY2008–REVISEDMAY2013 www.ti.com

The LVDS output buffers have features such as programmable LVDS currents, current doubling modes and

internal termination options. These can be used to widen eye openings and improve signal integrity, easing

capturebythereceiver.

TheADCchanneloutputscanbetransmittedeitherasMSBorLSBfirst and2scomplementorstraightbinary.

The ADS644X has internal references, but also can support an external reference mode. The device is specified

over–55°Cto125°Coperatingjunctiontemperaturerange.

2 SubmitDocumentationFeedback Copyright©2008–2013,TexasInstrumentsIncorporated

ProductFolderLinks:ADS6445-EPADS6444-EP

ADS6445-EP

ADS6444-EP

www.ti.com SLAS573C–FEBRUARY2008–REVISEDMAY2013

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriateprecautions.Failuretoobserveproperhandlingandinstallationprocedurescancausedamage.

ESDdamagecanrangefromsubtleperformancedegradationtocompletedevicefailure.Precisionintegratedcircuitsmaybemore

susceptibletodamagebecauseverysmallparametricchangescouldcausethedevicenottomeetitspublishedspecifications.

DD DD

AVDAGN CAP LVDLGN

BITClock DCLKP

DCLKM

CLKP PLL

CLKM

FRAMEClock FCLKP

FCLKM

DA0_P

INA_P Digital DA0_M

14 Bit Encoder

SHA ADC and DA1_P

INA_M Serializer

DA1_M

DB0_P

INB_P Digital DB0_M

14 Bit Encoder

SHA ADC and

DB1_P

INB_M Serializer

DB1_M

DC0_P

INC_P Digital DC0_M

14 Bit Encoder

SHA ADC and DC1_P

INC_M Serializer

DC1_M

DD0_P

IND_P Digital DD0_M

14 Bit Encoder

SHA ADC and DD1_P

IND_M Serializer

DD1_M

P M

F F

E E

R R

VCM Reference Parallel Serial

Interface Interface

ADS644x

DN G1 G2 G3 G4 EN TA LK ET

P CF CF CF CF S DA SC ES

S R

B0199-03

ORDERINGINFORMATION(1)

SPECIFIED

TRANSPORT

PACKAGE JUNCTION PACKAGE

PRODUCT PACKAGE-LEAD DESIGNATOR(2) TEMPERATURE MARKING ORDERINGNUMBER MEDIA, VIDNUMBER

QUANTITY

RANGE

ADS6445 6445EP ADS6445MRGCTEP V62/08628-01XE

QFN-64(3) RGC –55°Cto125°C 250,Tape/reel

ADS6444 6444EP ADS6444MRGCTEP V62/08628-02XE

(1) Forthemostcurrentpackageandorderinginformation,seethePackageOptionAddendumattheendofthisdocument,orseetheTI

websiteatwww.ti.com.

(2) Packagedrawings,thermaldata,andsymbolizationareavailableatwww.ti.com/packaging.

(3) Forthermalpadsizeonthepackage,seethemechanicaldrawingsattheendofthisdatasheet.θ =23.17°C/W(0LFMairflow),θ

JA JC

=22.1°C/Wwhenusedwith2oz.coppertraceandpadsoldereddirectlytoaJEDECstandardfourlayer3in.x3in.PCB.

Copyright©2008–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3

ProductFolderLinks:ADS6445-EPADS6444-EP

ADS6445-EP

ADS6444-EP

SLAS573C–FEBRUARY2008–REVISEDMAY2013 www.ti.com

ABSOLUTE MAXIMUM RATINGS(1)

VALUE UNIT

AVDD Supplyvoltagerange –0.3to3.9 V

LVDD Supplyvoltagerange –0.3to3.9 V

VoltagebetweenAGNDandDGND –0.3to0.3 V

VoltagebetweenAVDDtoLVDD –0.3to3.3 V

Voltageappliedtoexternalpin,VCM –0.3to2.0 V

Voltageappliedtoanaloginputpins –0.3Vtominimum(3.6,AVDD+0.3V) V

T Operatingjunctiontemperature 150 °C

J

T Storagetemperaturerange –65to150 °C

stg

Leadtemperature1,6mm(1/16")fromthecasefor10seconds 220 °C

(1) Stressesbeyondthoselistedunderabsolutemaximumratingsmaycausepermanentdamagetothedevice.Thesearestressratings

only,andfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderrecommendedoperating

conditionsisnotimplied.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability.

xxx

100.00

s)

ar

Ye

y ( 10.00

c

n

a

ct

e

p

x

E

e

m

eti

Lif

1.00

85 95 105 115 125 135 145

Junction Temperature, TJ(°C)

(1) Seedatasheetforabsolutemaximumandminimumrecommendedoperatingconditions.

(2) Silicon operating life design goal is 10 years at 105°C junction temperature (does not include package interconnect

life).

(3) Enhancedplasticproductdisclaimerapplies.

Figure1. LifetimeExpectancyGraphatElevatedTemperature

4 SubmitDocumentationFeedback Copyright©2008–2013,TexasInstrumentsIncorporated

ProductFolderLinks:ADS6445-EPADS6444-EP

ADS6445-EP

ADS6444-EP

www.ti.com SLAS573C–FEBRUARY2008–REVISEDMAY2013

THERMAL INFORMATION

ADS644x-EP

THERMALMETRIC(1) RGC UNITS

64PINS

θ Junction-to-ambientthermalresistance(2) 23.6

JA

θ Junction-to-case(top)thermalresistance(3) 7.7

JCtop

θ Junction-to-boardthermalresistance(4) 3

JB

°C/W

ψ Junction-to-topcharacterizationparameter(5) 0.1

JT

ψ Junction-to-boardcharacterizationparameter(6) 3

JB

θ Junction-to-case(bottom)thermalresistance(7) 0.3

JCbot

(1) Formoreinformationabouttraditionalandnewthermalmetrics,seetheICPackageThermalMetricsapplicationreport,SPRA953.

(2) Thejunction-to-ambientthermalresistanceundernaturalconvectionisobtainedinasimulationonaJEDEC-standard,high-Kboard,as

specifiedinJESD51-7,inanenvironmentdescribedinJESD51-2a.

(3) Thejunction-to-case(top)thermalresistanceisobtainedbysimulatingacoldplatetestonthepackagetop.NospecificJEDEC-

standardtestexists,butaclosedescriptioncanbefoundintheANSISEMIstandardG30-88.

(4) Thejunction-to-boardthermalresistanceisobtainedbysimulatinginanenvironmentwitharingcoldplatefixturetocontrolthePCB

temperature,asdescribedinJESD51-8.

(5) Thejunction-to-topcharacterizationparameter,ψ ,estimatesthejunctiontemperatureofadeviceinarealsystemandisextracted

JT

fromthesimulationdataforobtainingθ ,usingaproceduredescribedinJESD51-2a(sections6and7).

JA

(6) Thejunction-to-boardcharacterizationparameter,ψ ,estimatesthejunctiontemperatureofadeviceinarealsystemandisextracted

JB

fromthesimulationdataforobtainingθ ,usingaproceduredescribedinJESD51-2a(sections6and7).

JA

(7) Thejunction-to-case(bottom)thermalresistanceisobtainedbysimulatingacoldplatetestontheexposed(power)pad.Nospecific

JEDECstandardtestexists,butaclosedescriptioncanbefoundintheANSISEMIstandardG30-88.

Spacer

RECOMMENDED OPERATING CONDITIONS

overoperatingfree-airtemperaturerange(unlessotherwisenoted)

MIN NOM MAX UNIT

SUPPLIES

AVDD Analogsupplyvoltage 3.0 3.3 3.6 V

LVDD LVDSBuffersupplyvoltage 3.0 3.3 3.6 V

ANALOGINPUTS

Differentialinputvoltagerange 2 V

pp

Inputcommon-modevoltage 1.5±0.1 V

VoltageappliedonVCMinexternalreferencemode 1.45 1.50 1.55 V

CLOCKINPUT

ADS6445 5 125

Inputclocksamplerate,F MSPS

srated

ADS6444 5 105

Sinewave,accoupled 0.4 1.5

LVPECL,accoupled ±0.8

Inputclockamplitudedifferential(V –V ) V

CLKP CLKM pp

LVDS,accoupled ±0.35

LVCMOS,accoupled 3.3

InputClockdutycycle 35 50 65 %

DIGITALOUTPUTS

Maximumexternalloadcapacitancefromeachoutputpin Withoutinternaltermination 5

C pF

LOAD toDGND Withinternaltermination 10

R Differentialloadresistance(external)betweentheLVDSoutputpairs 100 Ω

LOAD

Copyright©2008–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5

ProductFolderLinks:ADS6445-EPADS6444-EP

ADS6445-EP

ADS6444-EP

SLAS573C–FEBRUARY2008–REVISEDMAY2013 www.ti.com

ELECTRICAL CHARACTERISTICS

Typicalvaluesareat25°C,minandmaxvaluesareacrossthefulljunctiontemperaturerangeT =–55°CtoT =

J,MIN J,MAX

125°C,AVDD=LVDD=3.3V,maximumratedsamplingfrequency,50%clockdutycycle,–1dBFSdifferentialanaloginput,

internalreferencemode(unlessotherwisenoted).

ADS6445 ADS6444

UNIT

PARAMETER Fs=125MSPS Fs=105MSPS

MIN TYP MAX MIN TYP MAX

RESOLUTION 14 14 Bits

ANALOGINPUT

Differentialinputvoltagerange 2.0 2.0 VPP

Differentialinputcapacitance 7 7 pF

Analoginputbandwidth 500 500 MHz

Analoginputcommonmodecurrent(perinputpin 155 130 μA

ofeachADC)

REFERENCEVOLTAGES

VREFB Internalreferencebottomvoltage 1.0 1.0 V

VREFT Internalreferencetopvoltage 2.0 2.0 V

ΔVREF Internalreferenceerror(VREFT–VREFB) 0.985 1 1.015 0.985 1 1.015 V

VCM Commonmodeoutputvoltage 1.5 1.5 V

VCMoutputcurrentcapability ±4 ±4 mA

DCACCURACY

Nomissingcodes Assured Assured

EO Offseterror,acrossdevicesandacrosschannels –15 ±2 15 –15 ±2 15 mV

withinadevice

Offseterrortemperaturecoefficient,across 0.05 0.05 mV/°C

devicesandacrosschannelswithinadevice

Therearetwosourcesofgainerror-internalreferenceinaccuracyandchannelgainerror

EGREF Gainerrorduetointernalreferenceinaccuracy -0.75 0.1 0.75 -0.75 0.1 0.75 %FS

alone,(ΔVREF/2.0)%

Referencegainerrortemperaturecoefficient 0.0125 0.0125 Δ%/°C

EGCHAN Gainerrorofchannelalone,acrossdevicesand ±0.3 ±0.3 %FS

acrosschannelswithinadevice

Channelgainerrortemperaturecoefficient,across 0.005 0.005 Δ%/°C

devicesandacrosschannelswithinadevice

DNL Differentialnonlinearity,Fin=50MHz –0.99 ±0.6 2.0 –0.99 ±0.6 2.0 LSB

INL Integralnonlinearity,Fin=50MHz -5 ±3 5 -5 ±3 5 LSB

PSRR DCpowersupplyrejectionratio 0.5 0.5 mV/V

POWERSUPPLY

ICC Totalsupplycurrent 502 410 mA

IAVDD Analogsupplycurrent 410 322 mA

ILVDD LVDSsupplycurrent 92 88 mA

Totalpower 1.65 1.8 1.35 1.5 W

Powerdown(withinputclockstopped) 77 150 77 150 mW

6 SubmitDocumentationFeedback Copyright©2008–2013,TexasInstrumentsIncorporated

ProductFolderLinks:ADS6445-EPADS6444-EP

ADS6445-EP

ADS6444-EP

www.ti.com SLAS573C–FEBRUARY2008–REVISEDMAY2013

ELECTRICAL CHARACTERISTICS

Typicalvaluesareat25°C,minandmaxvaluesareacrossthefulljunctiontemperaturerangeT =–55°CtoT =

J,MIN J,MAX

125°C,AVDD=LVDD=3.3V,maximumratedsamplingfrequency,50%clockdutycycle,–1dBFSdifferentialanaloginput,

internalreferencemode(unlessotherwisenoted).

ADS6445 ADS6444

PARAMETER TESTCONDITIONS Fs=125MSPS Fs=105MSPS UNIT

MIN TYP MAX MIN TYP MAX

DYNAMICACCHARACTERISTICS

Fin=10MHz 73.7 73.8

Fin=50MHz 68.5 73.1 73.2

Fin=70MHz 72.7 69 73

SNR Fin=100MHz 72.1 72.2

Signaltonoise dBFS

ratio 0dBgain 69.9 70.2

Fin=170MHz

3.5dBCoarsegain 69.4 69.7

0dBgain 68.7 68.8

Fin=230MHz

3.5dBCoarsegain 68.1 68.2

Fin=10MHz 73.4 73.4

Fin=50MHz 67.75 72.3 71.7

Fin=70MHz 71.2 68.5 72

SINAD

Signaltonoise Fin=100MHz 71.8 72

dBFS

anddistortion 0dBgain 67.9 69.8

ratio Fin=170MHz

3.5dBCoarsegain 68.3 69.3

0dBgain 67.8 67.7

Fin=230MHz

3.5dBCoarsegain 67.9 67.6

RMS Inputstiedtocommon-mode 1.05 1.05 LSB

Outputnoise

Fin=10MHz 87 91

Fin=50MHz 69 81 80

Fin=70MHz 78 74 81

SFDR Fin=100MHz 86 88

Spuriousfree dBc

dynamicrange 0dBgain 76 79

Fin=170MHz

3.5dBCoarsegain 79 83

0dBgain 77 77

Fin=230MHz

3.5dBCoarsegain 80 80

Fin=10MHz 93 94

Fin=50MHz 69 87 88

Fin=70MHz 87 74 88

HD2 Fin=100MHz 89 90

dBc

Secondharmonic 0dBgain 83 84

Fin=170MHz

3.5dBCoarsegain 85 86

0dBgain 80 81

Fin=230MHz

3.5dBCoarsegain 82 83

Fin=10MHz 87 91

Fin=50MHz 69 81 80

Fin=70MHz 78 74 81

HD3 Fin=100MHz 86 88

dBc

Thirdharmonic 0dBgain 76 79

Fin=170MHz

3.5dBCoarsegain 79 83

0dBgain 77 77

Fin=230MHz

3.5dBCoarsegain 80 80

Copyright©2008–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7

ProductFolderLinks:ADS6445-EPADS6444-EP

ADS6445-EP

ADS6444-EP

SLAS573C–FEBRUARY2008–REVISEDMAY2013 www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

Typicalvaluesareat25°C,minandmaxvaluesareacrossthefulljunctiontemperaturerangeT =–55°CtoT =

J,MIN J,MAX

125°C,AVDD=LVDD=3.3V,maximumratedsamplingfrequency,50%clockdutycycle,–1dBFSdifferentialanaloginput,

internalreferencemode(unlessotherwisenoted).

ADS6445 ADS6444

PARAMETER TESTCONDITIONS Fs=125MSPS Fs=105MSPS UNIT

MIN TYP MAX MIN TYP MAX

Fin=10MHz 91 91

Fin=50MHz 87 87

Worstharmonic

(otherthanHD2, Fin=100MHz 90 91 dBc

HD3)

Fin=170MHz 88 88

Fin=230MHz 87 87

Fin=10MHz 86 89.5

Fin=50MHz 69 80 80

THD

Totalharmonic Fin=100MHz 84.5 72 79 dBc

distortion

Fin=170MHz 73.5 86

Fin=230MHz 74 77

ENOB Fin=50MHz 10.95 11.7

Effectivenumber Bits

ofbits Fin=70MHz 11.3 11.7

IMD F1=46.09MHz, 88 90

2-Toneinter- F2=50.09MHz

dBFS

modulation F1=185.09MHz, 86 88

distortion F2=190.09MHz

Nearchannel 90 92

Cross-talksignal

frequency=10MHz

Cross-talk dBc

Farchannel 103 105

Cross-talksignal

frequency=10MHz

Inputoverload Recoverytowithin1%(offinalvalue)for6- 1 1 Clockcycles

recovery dBoverloadwithsinewaveinput

ACPSRR 35 35 dBc

Powersupply <100MHzsignal,100mVPPonAVDD

supply

rejectionratio

8 SubmitDocumentationFeedback Copyright©2008–2013,TexasInstrumentsIncorporated

ProductFolderLinks:ADS6445-EPADS6444-EP

ADS6445-EP

ADS6444-EP

www.ti.com SLAS573C–FEBRUARY2008–REVISEDMAY2013

DIGITAL CHARACTERISTICS

TheDCspecificationsrefertotheconditionwherethedigitaloutputsarenotswitching,butarepermanentlyatavalidlogic

level0or1AVDD=LVDD=3.3V,I =3.5mA,R =100Ω(1).

O LOAD

AllLVDSspecificationsarecharacterized,butnottestedatproduction.

ASD6445/ADS6444

PARAMETER TESTCONDITIONS UNIT

MIN TYP MAX

DIGITALINPUTS

High-levelinputvoltage 2.4 V

Low-levelinputvoltage 0.8 V

High-levelinputcurrent 10 μA

Low-levelinputcurrent 10 μA

Inputcapacitance 4 pF

DIGITALOUTPUTS

High-leveloutputvoltage 1375 mV

Low-leveloutputvoltage 1025 mV

Outputdifferentialvoltage|V | 250 350 450 mV

OD

OutputoffsetvoltageV Common-modevoltageofOUTPandOUTM 1200 mV

OS

Outputcapacitanceinsidethedevice,fromeitheroutputto 2 pF

Outputcapacitance

ground

(1) I referstotheLVDSbuffercurrentsetting,R istheexternaldifferentialloadresistancebetweentheLVDSoutputpair.

O LOAD

Copyright©2008–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9

ProductFolderLinks:ADS6445-EPADS6444-EP

ADS6445-EP

ADS6444-EP

SLAS573C–FEBRUARY2008–REVISEDMAY2013 www.ti.com

TIMING SPECIFICATIONS(1)

Typicalvaluesareat25°C,minandmaxvaluesareacrossthefulljunctiontemperaturerangeT =–55°CtoT =

J,MIN J,MAX

125°C,AVDD=LVDD=3.3V,maximumratedsamplingfrequency,sinewaveinputclock,1.5V clockamplitude,C =5

PP L

pF (2),I =3.5mA,R =100Ω (3),nointernaltermination,unlessotherwisenoted.

O L

ADS6445 ADS6444

PARAMETER TESTCONDITIONS Fs=125MSPS Fs=105MSPS UNIT

MIN TYP MAX MIN TYP MAX

tJ Aperturejitter Uncertaintyinthe 250 250 fsrms

samplinginstant

INTERFACE:2-wire,DDRbitclock,14xserialization

tsu Datasetuptime(4)(5)(6) Fbirtocmlodckatcarocsross-osv-oevrerto 0.55 0.65 ns

th Dataholdtime(4)(5)(6) Ftorodmatabictrcoloscsk-ocvreorss-over 0.58 0.7 ns

Inputclockrisingedge

Clockpropagationdelay

tpd_clk (6) cross-overtoframeclock 4.4 4.4 ns

risingedgecross-over

Bitclockcycle-cyclejitter

(5) 350 350 pspp

Frameclockcycle-cycle

jitter(5) 75 75 pspp

Thefollowingspecificationsapplyfor5MSPS≤Fs≤125MSPSandallinterfaceoptions.

Delayfrominputclock

tA Aperturedelay risingedgetotheactual 2 2 ns

samplinginstant

Channel-channelwithin

Aperturedelayvariation ±80 ±80 ps

samedevice

Timeforasampleto

ADCLatency(7) propagatetoADC 12 12 Clockcycles

outputs,seeFigure2

Timetovaliddataafter

comingoutofglobal 100 100 μs

powerdown

Timetovaliddataafter

Wakeuptime 100 100 μs

inputclockisre-started

Timetovaliddataafter

comingoutofchannel 200 200 Clockcycles

standby

tRISE Datarisetime From–100mVto+100 100 100 ps

mV

tFALL Datafalltime From+100mVto–100 100 100 ps

mV

Bitclockandframe From–100mVto+100

tRISE clockrisetime mV 100 100 ps

Bitclockandframe From+100mVto–100

tFALL clockfalltime mV 100 100 ps

LVDSBitclockduty

50% 50%

cycle

LVDSFrameclockduty

50% 50%

cycle

(1) Timingparametersareensuredbydesignandcharacterizationandnottestedinproduction.

(2) C istheexternalsingle-endedloadcapacitancebetweeneachoutputpinandground.

L

(3) I referstotheLVDSbuffercurrentsetting;R istheexternaldifferentialloadresistancebetweentheLVDSoutputpair.

o L

(4) Timingparametersaremeasuredattheendofa2inchPCBtrace(100Ωcharacteristicimpedance)terminatedbyR andC .

L L

(5) Setupandholdtimespecificationstakeintoaccounttheeffectofjitterontheoutputdataandclock.

(6) RefertoOutputTimingsinapplicationsectionfortimingsatlowersamplingfrequenciesandotherinterfaceoptions.

(7) Notethatthetotallatency=ADClatency+internalserializerlatency.Theserializerlatencydependsontheinterfaceoptionselectedas

showninTable27.

10 SubmitDocumentationFeedback Copyright©2008–2013,TexasInstrumentsIncorporated

ProductFolderLinks:ADS6445-EPADS6444-EP

Description:is a high performance 14 bit 125/105 MSPS quad channel A-D converter.

possible to halve the serial data rate (compared to a 1-wire interface) and restrict

it