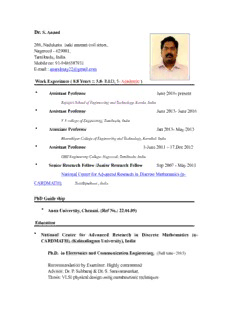

Table Of ContentDr. S. Anand

208, Nadukattu isaki amman coil street,

Nagercoil - 629001,

Tamilnadu, India.

Mobile no: 91-9486507911

E-mail : [email protected]

Work Experiance ( 8.8 Years :: 3.8- R&D, 5- Academic )

• Assistant Professor June 2016- present

Rajagiri School of Engineering and Technology, Kerala, India

• Assistant Professor June 2013- June 2016

V V college of Engineering, Tamilnadu, India

• Associate Professor Jan 2013- May 2013

Bharathiyar College of Engineering and Technology, Karaikal. India

• Assistant Professor 1-June 2011 – 17.Dec 2012

DMI Engineering College, Nagercoil, Tamilnadu, India

• Senior Research Fellow /Junior Research Fellow Sep 2007 - May 2011

National Center for Advanced Research in Discrete Mathematics (n-

CARDMATH), Srivilliputhoor , India

PhD Guide ship

• Anna University, Chennai. (Ref No.: 22.04.05)

Education

• National Center for Advanced Research in Discrete Mathematics (n-

CARDMATH), (Kalasalingam University), India

Ph.D. in Electronics and Communication Engineering, (Full time- 2013)

Recommendation by Examiner: Highly commented

Advisor: Dr. P. Subbaraj & Dr. S. Saravanasankar.

Thesis: VLSI physical design using metaheuristic techniques

• Arulmigu Kalasalingam College of Engineering (Anna University)

M.E. in VLSI Design, June 2007

Percentage: 76%

Adviser: Dr. P. Sivakumar

Thesis: Optimization of simulation based sequential circuit test automation

• St. Xaviers catholic college of engineering, (Anna University)

B.E. in Electronics and Communication Engineering, June 2005

Percentage: 74%

Adviser: Dr. J. Jeyasingh Thomas

Thesis: Maze solving robot using embedded system

Research Interests

• Algorithms design for industrial applications

• Evolutionary Algorithms and application.

• Biologically inspired heuristic design - parallel evolutionary algorithms.

• Physical Design of VLSI Circuits (VLSI CAD), especially Partitioning,

Floorplanning and Placement issues.

Fellowship

• DST Research Fellowship (Dept. of Science and Technology, Govt. of India) from n-

CARDMATH (National Center for Advance Research in Discrete Mathematics),

Kalasalingam University, Tamilnadu, India. During the period Sep 2007 - May 2011

(Project No : SR/S4/MS:326/06)

Awards

• Best Research Paper Award in International Conference on Advances in Industrial

Engineering Applications (ICAIEA-2010); Organized by Department of Industrial

Engineering, Anna University, Gundy, Chennai; on Jan 2010.

• Best Teacher Award from DMI Engineering College, Nagercoil, Tamilnadu; for

producing 92% students pass percentage during the semester July-Dec 2011.

• Certificate of Appreciation from VV College of engineering for the very good

academic performance for the years -2013, 2014, 2015, 2016.

As Journal Reviewer

• Reviewer, IEEE Transaction on Biomedical and Health Informatics.

• Reviewer, IEEE Transaction on Very Large Scale Integration Systems.

• Reviewer, J. Computers and Electrical Engineering, Elsevier Publishers.

• Reviewer, International Journal of Circuit Theory and Applications, Willy Publishers.

• Reviewer, International Journal of Manufacturing Engineering, Hindawi Publishers.

• Reviewer, Information Technology Research Journal.

Academic Publications

Book Chapter

1. P. Subbaraj, S. Saravanasankar and S. Anand, “Multi-Objective Optimization in

VLSI Floorplanning”, Communications in Computer and Information Science,

Springer publishers, Berlin Heidelberg, Volume 140, 65-72, 2011.

International Journal Papers

1. J. Jenifer and S. Anand, "Simulated Annealing Algorithm for Modern VLSI

Floorplanning Problem", ICTACT Journal on Microelectronics, April 2016, Volume:

02, Issue: 01.

2. M. Shunmugathammal, C. Christopher columbus and S. Anand, “A survey: on

various placers used in VLSI standard cell placement and mixed cell placement” int.

J. Chem. Sci.: 14(1), 2016, 1-9.

3. S. Anand, S. Saravanasankar and P. Subbaraj, “A multiobjective optimization tool for

Very Large Scale Integrated nonslicing floorplanning”, International Journal of

Circuit Theory and Applications. Volume 41, issue 9, Page: 904-923, Wiley

publishers, sep 2013, DOI: 10.1002/cta.829.

Quality Status: 2010 Impact factor: 1.759, ISI Journal Citation Reports® Thomson Reuters

Ranking: 2010: Engineering, Electrical & Electronic: 55 / 247 at Annexture1:3805

4. S. Anand, S. Saravanasankar and P. Subbaraj, “Customized Simulated Annealing

Based Decision Algorithms for Combinatorial Optimization in VLSI Floor planning

Problem”, Computational Optimization and Applications, Springer publishers,

Volume 52, Issue 3 (2012), Page 667-689, DOI 10.1007/s10589-011-9442-y.

Quality Status: 2010 Impact factor: 1.274, ISI Journal Citation Reports® Thomson Reuters

Ranking: 2010: Mathematics, applied: 52 / 235; at Annexture1:2002

5. P. Subbaraj, S. Saravanasankar and S. Anand, “Combinatorial Optimization in VLSI

Hypergraph Partitioning using Taguchi Methods”, International Journal of

Mathematical Combinotrics, Vol3, pp 69-84, 2010.

International Conference Proceedings

1.Jenifer J. and Anand S. , "An Efficient Algorithm for Modern VLSI Floorplanning

Problem", in Proceedings of International Conference on Current Trends in

Engineering Research, National Engineering College, Tirunelveli, pp. 38-45, 2016.

2.Jenifer J. and Anand S., "A Simulated Annealing Algorithm for VLSI

Floorplanning", in Proceedings of International Conference on Recent Advances in

Communication Systems and Technologies, Francis Xavier Engineering College,

Tirunelveli, pp. 62-73, 2016.

3.Lalin Laudis., Anand S., "Modified SA Algorithm for Wire length minimization in

VLSI circuits"., in. Proc. of IEEE International conference on circuit, power and

computing technologies., 19, 20 March 2015. Noorul Islam University, Nagercoil.

4.G.Dhivya., Anand S., "Implementation of Digital circuits in quantam dot cellular

automata"., in. Proc. of International Conference on Networks, Electronics,

Communication and Control system, march 2015, Cape instute of technology

5.Lalin L.Laudis, P.D. Saravanan, S. Anand & 4amit kumar sinha "AADHAR license

management (ALM) system in india using aadhar IDS"second national conference on

communication, information & control systems - 2015 (nccics'15) april 2015. VV

college of engineering,Thoothukudi.

6.Lalin Laudis, S. Anand, “FPGA Implementation : Smart Card Based License

Management using Iris Scanning Approach”, IEEE International Conference on

Science Engineering and Management Research (ICSEMR'14),. vol., no., pp.1,5,

27-29 Nov. 2014; Doi:10.1109/ICSEMR.2014.7043580; Vel Tech MultiTech Dr.

Rangarajan Dr. Sakunthala Engineering College, Avadi, Chennai, Tamilnadu, India.

7.P. Subbaraj, S. Saravanasankar and S. Anand, “Multi-Objective Optimization in VLSI

Floorplanning”, In proc. of International Conference on Logic, Information, Control

and Computation 2011, Gandhigram Rural Institute, TN, India, Feb 2011.

8.A. Aravindhan, S. Anand, P.S. Godwin Anand, “An analogous computation on hybrid

genetic algorithm for VLSI physical design specific to placement problem” Proceedings

of the International Conference on VLSI, Communication and Instrumentation [ICVCI-2011] ,

PP. 37-40, 2011, SAINTGITS College of Engg, Kottayam, INDIA.

9.P. Subbaraj, S. Saravanasankar and S. Anand, “Comparison of implicit data parallel

and sequential genetic algorithms for VLSI standard cell placement”, International

conference on advances in industrial engineering applications (ICAIEA-2010), DoIE,

Anna University, Gundy, Chennai on Jan 2010. (Awarded as the Best Paper of the

Conference )

10.P. Subbaraj, S. Saravanasankar, and S. Anand, “Parallel Genetic Algorithm for VLSI

Standard Cell Placement”, In Proceedings of the 2009 International Conference on

Advances in Computing, Control, and Telecommunication Technologies (ACT '09),

IEEE Computer Society, Washington, DC, USA, PP.80-84, 2009. DOI=10.1109/ACT.

2009.30 http://dx.doi.org/10.1109/ACT.2009.30

11.P. Subbaraj, S. Saravanasankar and S. Anand, “A new hybrid genetic algorithm for

VLSI circuit partitioning”, International conference on Intelligent Systems and Control

2009 (ISCO 2009), Karpagam University, 2009.

National Conference Proceedings

1.Jenifer J. and Anand S., "Optimization in VLSI Floorplanning", in proceedings of

national conference on Communication, Information and Control Systems

NCCICS’16, V V College Of Engineering, Tisaiyanvilai. Pp 22, 2016

2.C.Gracya, T.Kavitha, J.Muhideen Fathima Byrose & S. Anand "QCA implementation

of goldschmidt divider using data -tag method" in. Proc. of secound national

conference on communication information and control systems., april 2015. VV

college of engineering,Thoothukudi.

3. Leo Elstin. Lalin, L.Laudis & Anand S. "Study on b*tree for vlsi floorplanning"

in. Proc. of secound national conference on communication information and control

systems., april 2015. VV college of engineering,Thoothukudi.

4. Esakki Ponniah.R., Anand S., "Design and analysis of phase frequency detector

"., in. Proc. of secound national conference on communication information and control

systems., april 2015. VV college of engineering,Thoothukudi

5. G. Dhivya., Anand S., "Reversible logic based digital circuits realization using

quantum dot cellular automata "., in. Proc. of secound national conference on

communication information and control systems., april 2015. VV college of

engineering,Thoothukudi.

6. G. Dhivya., Anand S., "Efficient design of digital circuits in quantum dot cellular

automata” National Conference On Emerging Trends In Engineering And Technology-

EMTRENT'15, Jeyaraj Annapackiam C.S.I college of engineering, Nazareth

7. S. Anand, S. Jeyamalathi, s.shiny blessy, Studies on identifying less dead space in

VLSI floor planning, in. Proc. of secound national conference on communication

information and control systems, april 2014,VV college of engineering,Thoothukudi.

8. S. Anand and A. Aravindhan, “Multi-Warned Hybrid Genetic Algorithm for VLSI

Physical Design Specific to Placement Problem”, National Conference on

Microelectronics and Communication 2009 (NCMEC 2009)

9. S. Anand, P. Sivakumar “Optimization of simulation based sequential circuit test

automation”, National conference on resent trends in VLSI Design 2007

(NATCORN’07), Organized by Noorul Islam College of Engineering.

Communicated and under preparation papers

1. S. Anand “Lion – A Novel Non-dominated MOEA” (under preparation).

Research Experience

• Senior Research Fellow, n-CARDMATH (National Center for Advanced Research

in Discrete Mathematics)

Sep. 2009 to May 2011

o Designed tools for VLSI floorplanning and its constructional issues

o Designed multi objective tools for VLSI floorplanning

o Designed parallel computing tools for VLSI placement

• Junior Research Fellow, n-CARDMATH (National Center for Advanced Research

in Discrete Mathematics)

Sep. 2007 to Sep. 2009

o Provided a key role to the DST sponsored project “Combinatorial

Optimization in Packing Problems Specific to VLSI Design”

o Designed and developed a novel Evolutionary based algorithms to optimize

area in netlist partitioning

o Designed and developed algorithms for wirelength and area minimization in

layout floorplanning. Developed parallel evolutionary architectures.

Projects - During course

• PG -Project done during M.E course:

o Area of Project: VLSI testing

o Title : Optimization of simulation based sequential circuit test

automation.

o Duration : One year

o Description : A good fault simulator increases the speed of VLSI testing. Creation

of such efficient parallel fault simulator for synchronous sequential circuits is difficult.

HOPE is designed by updating PROOFS (a famous testing algorithm) and it is satisfying

the expectation and results efficient minimization of memory usage and it is 1.2 times

faster than older version of PROOF for ISCAS 89 benchmark circuits. The

implementations made using Linux based C.

• Project done during B.E course:

o Title : Maze solving Robot using embedded system.

o Duration : Three months

o Description : The robot can solve a maze automatically. Designed by using IR

sensors, stepper motors and Embedded System. Implemented by using PIC micro

controller.

Teaching and Advising Experience

I have taught the following courses at DMI Engineering College under Anna University

of Technology, Thirunelveali.

• Digital Electronics - July-Dec 2011 - Pass percentage (Pp) 78%

• Digital logic Circuits (Laboratory)

• Computer Architecture and Organization - July-Dec 2011- Pp. 92.5%

• Digital Logic Design - Jan-May 2012- Pp. 79%

• VLSI (Laboratory)

• Analog and Digital Communication, Embedded and Real time systems,

Communication theory.

I have taught the following courses at Bharathiyar College of Engineering and

Technology, Karaikal. India under Pondichery University.

• Utilization of Electrical Energy – Jan-may 2013

• Microcontroller and DSP based system design (PG) – Jan-may 2013

Project Guidence

I have Co-Advised and directed the following Post Graduate scholar projects:

• Multithreaded Hybrid Genetic Algorithm for VLSI Physical design specific to

Placement problem

• An Effective Memetic Algorithm for VLSI Placement Problem

• Multithreaded Memetic algorithm for VLSI Layout Floorplaning

• Hybrid Genetic approach for circuit partitioning

• Edge detection of images based on Genetic algorithm.

• Studies on multiobjective optimization and clustering.

I have advised the students not only from the current institution and also from the

neighboring institutions, especially students from IIT Kanpur

Intern Student Project:

• Student Name: Sandeep singh,

o Affiliation: 3rdYear Undergraduate, Department of Electrical Engineering, IIT Kanpur,

India, Area: Non dominated MOEA, Year: May 2013.

• Student Name: ASHISHDEWAKER,

o Affiliation: 3rdYear Undergraduate, Department of Electrical Engineering, IIT Kanpur,

India, Area: VLSI Floorplanning, Year: May 2012.

Technical Software Knowledge

• VLSI : Xilinx ISE, FPGA Boards

• VLSI EDA Tool : Cadence- SOC Encounter, Virtuoso (Analog and Digital IC

Design)

• Simulation tools: Matlab.

• Language : C, C++, VHDL, Verilog.

• Web Technologies: HTML.

• Operating systems: Solaris, Linux, Windows.

Packages Knowledge

• Latex

Additional Professional Skills

• Advance Diploma in Java Programming (From CSC Computer education), 2005

Professional Affiliations

• Association of Computer Electronics and Electrical Engineers (ACEEE) Member

International Research Collaboration

I have developed international research collaborations in the area of optimization with

• Dr. S. Sankar, (Not a Formal singed collaboration)

Senior Data Scientist, Solutions Development at Fusionex International.

Contribution in Grants and Proposals

• “Combinatorial Optimization in VLSI Gate Sizing and Threshold Voltage

Assignment” (Submitted on June 2015)

o Principal Investigator: Mr. S. Anand

o Funded By: Department of Science and Technology (DST), India

o Fund : Rs. 5,16,000

• Seminar: “Lecture Series on Computer Science, VLSI and Graph theory” 2011

o Funded By: DST- nCARDMATH, India

o Fund : Rs. 30,000

• “Combinatorial Optimization in Packing Problems Specific to VLSI Design” DST

project no: SR/S4/MS: 326/06, 2007 (completed – As Research Fellow)

o Principal Investigator: Dr. P. Subbaraj

o Co. Investigator: Dr. S. Saravanasanker

o Funded By: Department of Science and Technology (DST), India

o Contributed key sections to the proposal and yearly reports.

Professional Contributions

• Developed and maintaining website for n-CARDMATH Center

(www.ncardmath.com)

• Committee member in DST sponsored Plantinum jubilee 75th annual conference of

the Indian mathematical society (IMS)-2009

• Committee member in DST sponsored 5th International Workshop on Graph Labeling

2009 (IWOGL-2009)

• Committee member in DST sponsored International Conference on Discrete

Mathematics 2007 (ICDM-07)

Workshops Attended

• Attended two day ICTACT workhop on “People Empowering People” in PET

Engineering college during 24,25 july,14

• Attended one week workshop on “ Instructional work shop on Mathematical

Modeling and Simulation” in National center for advance Research in Discrete

Mathematics (n-CARDMATH) , Kalasalingam University, during July 07-14, 2010

• DST sponsored Instructional Workshop on Graph coloring at Kalasalingam

University, Krishnankoil, March 10-15, 2010.

• DST sponsored Instructional Workshop on Graph algorithm at Kalasalingam

University, Krishnankoil, February 17-24, 2010

• DST sponsored Instructional Workshop on introduction to Graph algorithm at

Kalasalingam University, Krishnankoil, February 3-6, 2010.

• Attended one week workshop on “ Instructional work shop on Introduction to Graph

Algorithms” in National center for advance Research in Discrete Mathematics (n-

CARDMATH), , Kalasalingam University during Feb 2010

• Attended one week workshop on “Optimizing Performance of Parallel Programs on

Emerging Multi-Core Processors & GPUs (OPECG-2009)” from Indian Institute of

Technology MADRAS ( IITM ), Chennai ,2009

• Attended one week workshop on “Optimization Techniques” from KLN College of

engineering; Madurai, 2009.

Conference / Seminars Attended

• DST Sponsored Research Oriented Lecture Series in Mathematics and Applications to

Engineering conducting by Department of Mathematics, Kalasalingam University, on

First and Third Saturdays of every month during the year 2007 to present.

• International conference on advances in industrial engineering applications

(icaiea-2010); organized by DoIE Anna University chennai on Jan 2010.

• International Conference on Advances in computing, control & Telecommunication

technologies 2009, Organized by ACEEE,

• Platinum Jubilee 75th Annual Conference of the Indian Mathematical Society at

Kalasalingam University, Krishnankoil, December 27-30, 2009.

• International conference on intelligent systems and Control 2009 (ISCO 2009),

Organized by Karpagam University.

• Fifth International Workshop on Graph Labelings (IWOGL 2009) at Kalasalingam

University, Krishnankoil, January 07-10, 2009 (Sponsored by Department of Science

and Technology, New Delhi and Indo-US Science and Technology Forum, New

Delhi)

Description:“Combinatorial Optimization in VLSI. Hypergraph Partitioning using Taguchi Methods”, International Journal of. Mathematical Combinotrics, Vol3, pp