Table Of ContentProduct Order Technical Tools & Support & Reference

Folder Now Documents Software Community Design

ADS8588S

SBAS642A–DECEMBER2016–REVISEDAPRIL2017

ADS8588S 16-Bit, High-Speed, 8-Channel, Simultaneous-Sampling ADC with

Bipolar Inputs on a Single Supply

1 Features 3 Description

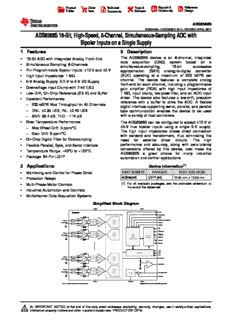

• 16-Bit ADCwithIntegratedAnalogFront-End The ADS8588S device is an 8-channel, integrated

1 data acquisition (DAQ) system based on a

• SimultaneousSampling:8-Channels

simultaneous-sampling, 16-bit successive

• Pin-ProgrammableBipolarInputs:±10Vand ±5V approximation (SAR) analog-to-digital converter

• HighInputImpedance:1MΩ (ADC) operating at a maximum of 200 kSPS per

channel. The device features a complete analog

• 5-VAnalogSupply:2.3-Vto5-V I/OSupply

front-end for each channel, including a programmable

• OvervoltageInputClampwith7-kVESD gain amplifier (PGA) with high input impedance of

• Low-Drift,On-ChipReference(2.5V)andBuffer 1 MΩ, input clamp, low-pass filter, and an ADC input

driver. The device also features a low-drift, precision

• ExcellentPerformance:

reference with a buffer to drive the ADC. A flexible

– 200-kSPSMaxThroughputonAllChannels

digitalinterfacesupportingserial, parallel,and parallel

– DNL: ±0.35LSB;INL: ±0.45LSB byte communication enables the device to be used

– SNR: 96.4dB;THD: −114dB withavarietyofhostcontrollers.

• OverTemperaturePerformance: The ADS8588S can be configured to accept ±10-V or

±5-V true bipolar inputs using a single 5-V supply.

– MaxOffsetDrift:3ppm/°C

The high input impedance allows direct connection

– GainDrift:6ppm/°C

with sensors and transformers, thus eliminating the

• On-ChipDigital FilterforOversampling need for external driver circuits. The high

• FlexibleParallel,Byte,andSerialInterface performance and accuracy, along with zero-latency

conversions offered by this device, also make the

• TemperatureRange:–40°Cto+125°C

ADS8588S a great choice for many industrial

• Package:64-PinLQFP automationandcontrolapplications.

2 Applications DeviceInformation(1)

• MonitoringandControlforPowerGrids PARTNUMBER PACKAGE BODYSIZE(NOM)

• ProtectionRelays ADS8588S LQFP(64) 10.00mm×10.00mm

• Multi-PhaseMotorControls (1) For all available packages, see the orderable addendum at

theendofthedatasheet.

• IndustrialAutomationandControls

• MultichannelDataAcquisitionSystems

SimplifiedBlockDiagram

AVDD DVDD

ADS8588S BUSY

FRSTDATA

STBY

AINA_I1NG_N1DP CCllaammpp 1 M: PGA 3rdL-OPFrder ADDrivCer 1AS6DA-BRCit RCEOSNEVTSTA, CONVSTB

1 M: RANGE

CS

1 M: RD/SCLK

AINA_I2NG_N2DP CCllaammpp 1 M: PGA 3rdL-OPFrder ADDrivCer 1AS6DA-BRCit DigitLaSaol AnCgdRioc n trol SInEtRer/fPaAceR PDABR[1/5S:E0R]

DOUTA

DOUTB

OS0

Digital Filter OS1

1 M: OS2

AINA_I7NG_N7DP CCllaammpp PGA 3rdL-OPFrder ADDrivCer 1AS6DA-BRCit REFCAPA

1 M:

REFCAPB

1 M:

AINA_I8NG_N8DP CCllaammpp 1 M: PGA 3rdL-OPFrder ADDrivCer 1AS6DA-BRCit 2.5 VREF REFIN/REFOUT

REFSEL

AGND REFGND DGND

NOTE: There are 8 channels for the ADS8588S. Copyright © 2017, Texas Instruments Incorporated

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

ADS8588S

SBAS642A–DECEMBER2016–REVISEDAPRIL2017 www.ti.com

Table of Contents

1 Features.................................................................. 1 7.17 SwitchingCharacteristics:ParallelDataRead

Operation,CSandRDSeparate.............................14

2 Applications........................................................... 1

7.18 SwitchingCharacteristics:SerialDataRead

3 Description............................................................. 1

Operation.................................................................14

4 RevisionHistory..................................................... 2

7.19 SwitchingCharacteristics:ByteModeDataRead

5 DeviceFamilyComparisonTable........................ 4 Operation.................................................................14

6 PinConfigurationandFunctions......................... 4 7.20 TypicalCharacteristics..........................................18

7 Specifications......................................................... 6 8 DetailedDescription............................................ 25

7.1 AbsoluteMaximumRatings......................................6 8.1 Overview.................................................................25

7.2 ESDRatings..............................................................7 8.2 FunctionalBlockDiagram.......................................25

7.3 RecommendedOperatingConditions.......................7 8.3 FeatureDescription.................................................26

7.4 ThermalInformation..................................................7 8.4 DeviceFunctionalModes........................................34

7.5 ElectricalCharacteristics...........................................8 9 ApplicationandImplementation........................ 47

7.6 TimingRequirements:CONVSTControl................11 9.1 ApplicationInformation............................................47

7.7 TimingRequirements:DataReadOperation..........11 9.2 TypicalApplication..................................................47

7.8 TimingRequirements:ParallelDataReadOperation, 10 PowerSupplyRecommendations..................... 51

CSandRDTiedTogether.......................................11

11 Layout................................................................... 52

7.9 TimingRequirements:ParallelDataReadOperation,

11.1 LayoutGuidelines.................................................52

CSandRDSeparate...............................................12

11.2 LayoutExample....................................................52

7.10 TimingRequirements:SerialDataRead

Operation.................................................................12 12 DeviceandDocumentationSupport................. 54

7.11 TimingRequirements:ByteModeDataRead 12.1 DocumentationSupport........................................54

Operation.................................................................12 12.2 ReceivingNotificationofDocumentationUpdates54

7.12 TimingRequirements:OversamplingMode..........12 12.3 CommunityResources..........................................54

7.13 TimingRequirements:ExitStandbyMode............12 12.4 Trademarks...........................................................54

7.14 TimingRequirements:ExitShutdownMode.........13 12.5 ElectrostaticDischargeCaution............................54

7.15 SwitchingCharacteristics:CONVSTControl........13 12.6 Glossary................................................................54

7.16 SwitchingCharacteristics:ParallelDataRead 13 Mechanical,Packaging,andOrderable

Operation,CSandRDTiedTogether.....................13 Information........................................................... 54

4 Revision History

NOTE:Pagenumbersforpreviousrevisionsmaydifferfrompagenumbersinthecurrentversion.

ChangesfromOriginal(December2016)toRevisionA Page

• DeletedADS8586SandADS8584Sfromdocument............................................................................................................. 1

• Changeddocumenttitle.......................................................................................................................................................... 1

• ChangedfirsttwosentencesofDescriptionsection.............................................................................................................. 1

• ChangedSimplifiedBlockDiagramfigure:changed2nd-orderto3rd-orderandRANGE/SDItoRANGEinfigure,

addedtitle............................................................................................................................................................................... 1

• ChangedDeviceFamilyComparisonTabletocomparedevicefamilymembers.................................................................. 4

• ChangedAGNDtoDGNDinDVDDtoDGNDrowofAbsoluteMaximumRatingstable...................................................... 6

• Changedminimumspecificationfrom–96to–64inlastrowofexternalreferenceforE parameter ................................. 8

G

• Changedx-axisofDCHistogramofCodes(±10V),DCHistogramofCodes(±5V),andDNLforAllCodescurves.......18

• Changedx-axisofINLvsAllCodes(±10V)andINLvsAllCodes(±5V)curves.............................................................. 19

• Changedsecond-ordertothird-orderinfirstparagraphofOverviewsection ..................................................................... 25

• Changed2nd-orderto3rd-orderandRANGE/SDItoRANGEinfunctionalblockdiagram................................................. 25

• Changed2nd-orderto3rd-orderinFront-EndCircuitSchematicforEachAnalogInputChannelfigure............................ 26

• ChangedmultipletotwoinfirstsentenceofsecondparagraphofAnalogInputssection.................................................. 26

• ChangedsecondtothirdintitleanddescriptionofThird-Order,Low-PassFilter(LPF)section......................................... 28

• AddedButterworthtoLPFdescriptioninThird-Order,Low-PassFilter(LPF)section......................................................... 28

• ChangedsecondtothirdintitlesofThird-OrderLPFMagnitudeResponseandThird-OrderLPFPhaseResponse

figures................................................................................................................................................................................... 28

2 SubmitDocumentationFeedback Copyright©2016–2017,TexasInstrumentsIncorporated

ProductFolderLinks:ADS8588S

ADS8588S

www.ti.com SBAS642A–DECEMBER2016–REVISEDAPRIL2017

Revision History (continued)

• Changed16-BitADCTransferFunction(TwosComplementBinaryFormat)figureformoreaccuraterepresentation......33

• ChangedconversiontoconversionresultsinfirstsentenceofthirdparagraphinSerialDataReadsection.....................42

• Changedx-axisofcurvesDCHistogramforOSR2toDCHistogramforOSR64............................................................... 45

• Changed2nd-orderto3rd-orderin8-ChannelDAQforPowerAutomationUsingtheADS8588Sfigure........................... 47

• Changed2nd-orderto3rd-orderinInputRCLow-PassFilterfigure................................................................................... 48

• DeletedPSRRAcrossFrequency(WithoutDecapacitor)figurefromPowerSupplyRecommendationssection...............51

• ChangedPSRRAcrossFrequency(WithDecapacitor)figure ............................................................................................ 51

Copyright©2016–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3

ProductFolderLinks:ADS8588S

ADS8588S

SBAS642A–DECEMBER2016–REVISEDAPRIL2017 www.ti.com

5 Device Family Comparison Table

PRODUCT RESOLUTION(Bits) CHANNELS SAMPLERATE(kSPS)

ADS8588S 16 8,single-ended 200

ADS8586S 16 6,single-ended 250

ADS8584S 16 4,single-ended 330

ADS8578S 14 8,single-ended 200

6 Pin Configuration and Functions

PMPackage:ADS8588S

64-PinLQFP

TopView

D D D D D D D D

N N N N N N N N

G P G P G P G P G P G P G P G P

8 8 7 7 6 6 5 5 4 4 3 3 2 2 1 1

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

N N N N N N N N N N N N N N N N

AI AI AI AI AI AI AI AI AI AI AI AI AI AI AI AI

4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9

6 6 6 6 6 5 5 5 5 5 5 5 5 5 5 4

AVDD 1 48 AVDD

AGND 2 47 AGND

OS0 3 46 REFGND

OS1 4 45 REFCAPB

OS2 5 44 REFCAPA

PAR/SER/BYTE SEL 6 43 REFGND

STBY 7 42 REFIN/REFOUT

RANGE 8 41 AGND

CONVSTA 9 40 AGND

CONVSTB 10 39 REGCAP2

RESET 11 38 AVDD

RD/SCLK 12 37 AVDD

CS 13 36 REGCAP1

BUSY 14 35 AGND

FRSTDATA 15 34 REFSEL

DB0 16 33 DB15/BYTE SEL

7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2

1 1 1 2 2 2 2 2 2 2 2 2 2 3 3 3

1 2 3 4 5 6 D A B D 9 0 1 2 3 N

DB DB DB DB DB DB DVD OUT OUT AGN DB DB1 DB1 DB1 DB1 HBE Not to scale

B7/D B8/D B14/

D D D

4 SubmitDocumentationFeedback Copyright©2016–2017,TexasInstrumentsIncorporated

ProductFolderLinks:ADS8588S

ADS8588S

www.ti.com SBAS642A–DECEMBER2016–REVISEDAPRIL2017

PinFunctions

PIN

TYPE(1) DESCRIPTION

NAME NO.

AGND 2,26,35,40,41,47 P Analoggroundpins

AIN_1GND 50 AI Analoginputchannel1:negativeinput

AIN_1P 49 AI Analoginputchannel1:positiveinput

AIN_2GND 52 AI Analoginputchannel2:negativeinput

AIN_2P 51 AI Analoginputchannel2:positiveinput

AIN_3GND 54 AI Analoginputchannel3:negativeinput

AIN_3P 53 AI Analoginputchannel3:positiveinput

AIN_4GND 56 AI Analoginputchannel4:negativeinput

AIN_4P 55 AI Analoginputchannel4:positiveinput

AIN_5GND 58 AI Analoginputchannel5:negativeinput

AIN_5P 57 AI Analoginputchannel5:positiveinput

AIN_6GND 60 AI Analoginputchannel6:negativeinput

AIN_6P 59 AI Analoginputchannel6:positiveinput

AIN_7GND 62 AI Analoginputchannel7:negativeinput

AIN_7P 61 AI Analoginputchannel7:positiveinput

AIN_8GND 64 AI Analoginputchannel8:negativeinput

AIN_8P 63 AI Analoginputchannel8:positiveinput

Analogsupplypins.DecouplethesepinstotheclosestAGNDpins

AVDD 1,37,38,48 P

(seethePowerSupplyRecommendationssection)

Activehighdigitaloutputindicatingongoingconversion

BUSY 14 DO

(seetheBUSY(Output)section)

Activehighlogicinputtocontrolstartofconversionforfirsthalfcountofdeviceinput

CONVSTA 9 DI

channels(seetheCONVSTA,CONVSTB(Input)section)

Activehighlogicinputtocontrolstartofconversionforsecondhalfcountofdeviceinput

CONVSTB 10 DI

channels(seetheCONVSTA,CONVSTB(Input)section)

CS 13 DI Activelowlogicinputchip-selectsignal(seetheCS(Input)section)

DB0 16 DO DataoutputDB0(LSB)inparallelinterfacemode(seetheDB[6:0]section)

DB1 17 DO DataoutputDB1inparallelinterfacemode(seetheDB[6:0]section)

DB2 18 DO DataoutputDB2inparallelinterfacemode(seetheDB[6:0]section)

DB3 19 DO DataoutputDB3inparallelinterfacemode(seetheDB[6:0]section)

DB4 20 DO DataoutputDB4inparallelinterfacemode(seetheDB[6:0]section)

DB5 21 DO DataoutputDB5inparallelinterfacemode(seetheDB[6:0]section)

DB6 22 DO DataoutputDB6inparallelinterfacemode(seetheDB[6:0]section)

Multi-functionlogicoutputpin(seetheDB7/DOUTAsection):

DB7/DOUTA 24 DO thispinisdataoutputDB7inparallelandparallelbyteinterfacemode;

thispinisadataoutputpininserialinterfacemode.

Multi-functionlogicoutputpin(seetheDB8/DOUTBsection):

DB8/DOUTB 25 DO thispinisdataoutputDB8inparallelinterfacemode;

thispinisadataoutputpininserialinterfacemode.

DB9 27 DO DataoutputDB9inparallelinterfacemode(seetheDB[13:9]section)

DB10 28 DO DataoutputDB10inparallelinterfacemode(seetheDB[13:9]section)

DB11 29 DO DataoutputDB11inparallelinterfacemode(seetheDB[13:9]section)

DB12 30 DO DataoutputDB12inparallelinterfacemode(seetheDB[13:9]section)

DB13 31 DO DataoutputDB13inparallelinterfacemode(seetheDB[13:9]section)

Multi-functionlogicinputoroutputpin(seetheDB14/HBENsection):

DB14/HBEN 32 DIO thispinisdataoutputDB14inparallelinterfacemode;

thispinisacontrolinputpinforbyteselection(highorlow)inparallelbyteinterfacemode

Multi-functionlogicinputoroutputpin(seetheDB15/BYTESELsection):

DB15/BYTESEL 33 DIO thispinisdataoutputDB15(MSB)inparallelinterfacemode;

thispinisanactivehighcontrolinputpintoenableparallelbyteinterfacemode.

DVDD 23 P Digitalsupplypin;decouplewithAGNDonpin26.

Activehighdigitaloutputindicatingdatareadbackfromchannel1ofthedevice(seethe

FRSTDATA 15 DO

FRSTDATA(Output)section)

(1) AI=analoginput;AO=analogoutput;AIO=analoginput/output;DI=digitalinput;DO=digitaloutput;DIO=digitalinput/output;P=

powersupply;andNC=noconnect.

Copyright©2016–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5

ProductFolderLinks:ADS8588S

ADS8588S

SBAS642A–DECEMBER2016–REVISEDAPRIL2017 www.ti.com

PinFunctions (continued)

PIN

TYPE(1) DESCRIPTION

NAME NO.

Oversamplingmodecontrolpin

OS0 3 DI

(seetheOversamplingModeofOperationsection)

Oversamplingmodecontrolpin

OS1 4 DI

(seetheOversamplingModeofOperationsection)

Oversamplingmodecontrolpin

OS2 5 DI

(seetheOversamplingModeofOperationsection)

Logicinputpintoselectbetweenparallel,serial,orparallelbyteinterfacemode(seethe

PAR/SER/BYTESEL 6 DI

DataReadOperationsection)

Multi-functionlogicinputpin(seetheRANGE(Input)section):

RANGE 8 DI whenSTBYpinishigh,thispinselectstheinputrangeofthedevice(±10Vor±5V);when

STBYpinislow,thispinselectsbetweenthestandbyandshutdownmodes.

Multi-functionlogicinputpin(seetheRD/SCLK(Input)section):

RD/SCLK 12 DI thispinisanactive-lowreadyinputpininparallelandparallelbyteinterface;

thispinisaclockinputpininserialinterfacemode.

Referenceamplifieroutputpins.ThispinmustbeshortedtoREFCAPBanddecoupledto

REFCAPA 44 AO

AGNDusingalowESR,10-µFceramiccapacitor.

Referenceamplifieroutputpins.ThispinmustbeshortedtoREFCAPAanddecoupledto

REFCAPB 45 AO

AGNDusingalowESR,10-µFceramiccapacitor.

ReferenceGNDpin.ThispinmustbeshortedtotheanalogGNDplaneanddecoupledwith

REFGND 43,46 P

REFIN/REFOUTonpin42usinga10-µFcapacitor.

ThispinactsasaninternalreferenceoutputwhenREFSELishigh;

REFIN/REFOUT 42 AIO thispinfunctionsasinputpinfortheexternalreferencewhenREFSELislow;

decouplewithREFGNDonpin43usinga10-µFcapacitor.

Activehighlogicinputtoenabletheinternalreference

REFSEL 34 DI

(seetheREFSEL(Input)section)

Outputpin1fortheinternalvoltageregulator;decoupleseparatelytoAGNDusinga1-µF

REGCAP1 36 AO

capacitor.

Outputpin2fortheinternalvoltageregulator;decoupleseparatelytoAGNDusinga1-µF

REGCAP2 39 AO

capacitor.

Activehighlogicinputtoresetthedevicedigitallogic

RESET 11 DI

(seetheRESET(Input)section)

Activelowlogicinputtoenterthedeviceintooneofthetwopower-downmodes:standbyor

STBY 7 DI

shutdown(seethePower-DownModessection)

7 Specifications

7.1 Absolute Maximum Ratings

atT =25°C(unlessotherwisenoted)(1)

A

MIN MAX UNIT

AVDDtoAGND –0.3 7.0 V

DVDDtoDGND –0.3 7.0 V

AGNDtoDGND –0.3 0.3 V

AnaloginputvoltagetoAGND(2) –15 15 V

DigitalinputtoDGND –0.3 DVDD+0.3 V

REFINtoAGND –0.3 AVDD+0.3 V

Inputcurrenttoanypinexceptsupplies(2) –10 10 mA

Operating –40 125

Temperature Junction,T 150 °C

J

Storage,T –65 150

stg

(1) StressesbeyondthoselistedunderAbsoluteMaximumRatingsmaycausepermanentdamagetothedevice.Thesearestressratings

only,whichdonotimplyfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderRecommended

OperatingConditions.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability.

(2) Transientcurrentsofupto100mAdonotcauseSCRlatch-up.

6 SubmitDocumentationFeedback Copyright©2016–2017,TexasInstrumentsIncorporated

ProductFolderLinks:ADS8588S

ADS8588S

www.ti.com SBAS642A–DECEMBER2016–REVISEDAPRIL2017

7.2 ESD Ratings

VALUE UNIT

Human-bodymodel(HBM),per Allpinsexceptanaloginputs ±2000

ANSI/ESDA/JEDECJS-001(1) Analoginputpinsonly ±7000

V Electrostaticdischarge V

(ESD)

Charged-devicemodel(CDM),perJEDEC

specificationJESD22-C101(2) Allpins ±500

(1) JEDECdocumentJEP155statesthat500-VHBMallowssafemanufacturingwithastandardESDcontrolprocess.

(2) JEDECdocumentJEP157statesthat250-VCDMallowssafemanufacturingwithastandardESDcontrolprocess.

7.3 Recommended Operating Conditions

overoperatingfree-airtemperaturerange(unlessotherwisenoted)

MIN NOM MAX UNIT

AVDD Analogsupplyvoltage 4.75 5 5.25 V

DVDD Digitalsupplyvoltage 2.3 3.3 AVDD V

7.4 Thermal Information

ADS8588S

THERMALMETRIC(1) PM(LQFP) UNIT

64PINS

R Junction-to-ambientthermalresistance 46.0 °C/W

θJA

R Junction-to-case(top)thermalresistance 7.8 °C/W

θJC(top)

R Junction-to-boardthermalresistance 20.1 °C/W

θJB

ψ Junction-to-topcharacterizationparameter 0.3 °C/W

JT

ψ Junction-to-boardcharacterizationparameter 19.6 °C/W

JB

R Junction-to-case(bottom)thermalresistance N/A °C/W

θJC(bot)

(1) Formoreinformationabouttraditionalandnewthermalmetrics,seetheSemiconductorandICPackageThermalMetricsapplication

report.

Copyright©2016–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7

ProductFolderLinks:ADS8588S

ADS8588S

SBAS642A–DECEMBER2016–REVISEDAPRIL2017 www.ti.com

7.5 Electrical Characteristics

minimumandmaximumspecificationsareatT =–40°Cto+125°C,AVDD=4.75Vto5.25V;typicalspecificationsareatT

A A

=25°C;AVDD=5V,DVDD=3V,V =2.5V(internal),andf =200kSPS(unlessotherwisenoted)

REF SAMPLE

TEST

PARAMETER TESTCONDITIONS MIN TYP MAX UNIT LEVEL(1)

ANALOGINPUTS

Full-scaleinputspan(2) RANGEpin=1 –10 10 A

V

(AIN_nPtoAIN_nGND) RANGEpin=0 –5 5 A

Operatinginputrange, RANGEpin=1 –10 10 A

AIN_nP V

positiveinput RANGEpin=0 –5 5 A

Operatinginputrange,

AIN_nGND Allinputranges –0.3 0 0.3 V B

negativeinput

RIN Inputimpedance AtTA=25°C 0.85 1 1.15 MΩ B

Inputimpedancedrift Allinputranges –25 ±7 25 ppm/°C B

IIkg(in) Inputleakagecurrent WallitihnpvuotltraagnegeastAIN_nP=VIN, (VIN–2)/RIN µA A

SYSTEMPERFORMANCE

Resolution 16 Bits A

NMC Nomissingcodes 16 Bits A

DNL Differentialnonlinearity Allinputranges –0.5 ±0.35 0.5 LSB(3) A

INL Integralnonlinearity(4) Allinputranges –1.5 ±0.45 1.5 LSB A

Allinput TA=–40°Cto –64 ±4 64 A

ranges, +85°C

EG Gainerror(5) erexfteerrennacle T+1A2=5–°C40°Cto –64 ±4 96 LSB A

Allinputranges,

±4 A

internalreference

Inputrange=±10V,

10 60 A

Gainerrormatching externalandinternalreference

LSB

(channel-to-channel) Inputrange=±5V,

12 60 A

externalandinternalreference

Allinputranges,

–14 ±6 14 B

externalreference

Gainerrortemperaturedrift ppm/°C

Allinputranges,

±10 B

internalreference

Inputrange=±10V –1.8 ±0.15 1.8 B

EO Offseterror mV

Inputrange=±5V –1.8 ±0.15 1.8 B

Offseterrormatching

Allinputranges 0.3 2.4 mV B

(channel-to-channel)

Offseterrortemperaturedrift Allinputranges –3 ±0.3 3 ppm/°C B

SAMPLINGDYNAMICS

tACQ Acquisitiontime 1 µs A

Maximumthroughputrateperchannel

fS withoutlatency Alleightchannelsincluded 200 kSPS A

(1) TestLevels:(A)Testedatfinaltest.Overtemperaturelimitsaresetbycharacterizationandsimulation.(B)Limitssetbycharacterization

andsimulation,acrosstemperaturerange.(C)Typicalvalueonlyforinformation,providedbydesignsimulation.

(2) Idealinputspan,doesnotincludegainoroffseterror.

(3) LSB=leastsignificantbit.

(4) ThisparameteristheendpointINL,notbest-fitINL.

(5) Gainerroriscalculatedafteradjustingforoffseterror,whichimpliesthatpositivefull-scaleerror=negativefull-scaleerror=gainerror÷

2.

8 SubmitDocumentationFeedback Copyright©2016–2017,TexasInstrumentsIncorporated

ProductFolderLinks:ADS8588S

ADS8588S

www.ti.com SBAS642A–DECEMBER2016–REVISEDAPRIL2017

Electrical Characteristics (continued)

minimumandmaximumspecificationsareatT =–40°Cto+125°C,AVDD=4.75Vto5.25V;typicalspecificationsareatT

A A

=25°C;AVDD=5V,DVDD=3V,V =2.5V(internal),andf =200kSPS(unlessotherwisenoted)

REF SAMPLE

TEST

PARAMETER TESTCONDITIONS MIN TYP MAX UNIT LEVEL(1)

DYNAMICCHARACTERISTICS

Signal-to-noiseratio, Inputrange=±10V 91 92.7 A

SNR nooversampling dB

(VIN–0.5dBFSat1kHz) Inputrange=±5V 90.4 92.2 A

Signal-to-noiseratio, Inputrange=±10V 95.5 96.4 A

SNROSR oversampling=16x dB

(VIN–0.5dBFSat130Hz) Inputrange=±5V 94.4 95.5 A

Totalharmonicdistortion(6)

THD Allinputranges –114 –95 dB B

(VIN–0.5dBFSat1kHz)

Signal-to-noise+distortionratio, Inputrange=±10V 90.7 92.7 A

SINAD nooversampling dB

(VIN–0.5dBFSat1kHz) Inputrange=±5V 90.2 92.1 A

Signal-to-noise+distortionratio, Inputrange=±10V 95 96.4 A

SINADOSR oversampling=16x dB

(VIN–0.5dBFSat130Hz) Inputrange=±5V 94 95.4 A

Spurious-freedynamicrange

SFDR Allinputranges –118 dB B

(VIN–0.5dBFSat1kHz)

Crosstalkisolation(7) –95 dB A

AtTA=25°C, 24 B

inputrange=±10V

BW(–3dB) –3dB kHz

AtTA=25°C, 16 B

Small-signal inputrange=±5V

bandwidth AtTA=25°C, 14 B

inputrange=±10V

BW(–0.1dB) –0.1dB kHz

AtTA=25°C, 9.5 B

inputrange=±5V

Inputrange=±10V 13 C

tGROUP Groupdelay µs

Inputrange=±5V 19 C

INTERNALREFERENCEOUTPUT(REFSEL=1)

VREF(8) V(coolntafiggeuroendtahseoRuEtpFuINt)/REFOUTpin AtTA=25°C 2.4975 2.5 2.5025 V A

Internalreferencetemperaturedrift 7.5 ppm/°C B

Decouplingcapacitoron

C(REFIN_REFOUT) REFIN/REFOUT(9) 10 µF B

ReferencevoltagetotheADC

V(REFCAP) (ontheREFCAPA,REFCAPBpin) AtTA=25°C 3.996 4.0 4.004 V A

Referencebufferoutputimpedance 0.5 1 Ω C

Referencebufferoutputtemperature

5 ppm/°C B

drift

DecouplingcapacitoronREFCAPA,

C(REFCAP) REFCAPB 10 µF B

Turn-ontime C(REFCAP)=10µF, 25 ms B

C(REFIN_REFOUT)=10µF

EXTERNALREFERENCEINPUT(REFSEL=0)

ExternalreferencevoltageonREFIO

VREFIO_EXT (configuredasinput) 2.475 2.5 2.525 V B

Referenceinputimpedance 100 MΩ C

Referenceinputcapacitance 10 pF C

(6) Calculatedonthefirstnineharmonicsoftheinputfrequency.

(7) Isolationcrosstalkismeasuredbyapplyingafull-scalesinusoidalsignalupto160kHztoachannel,notselectedinthemultiplexing

sequence,andmeasuringtheeffectontheoutputofanyselectedchannel.

(8) Doesnotincludethevariationinvoltageresultingfromsoldershifteffects.

(9) RecommendedtouseanX7R-grade,0603-sizeceramiccapacitorforoptimumperformance(seetheLayoutGuidelinessection).

Copyright©2016–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9

ProductFolderLinks:ADS8588S

ADS8588S

SBAS642A–DECEMBER2016–REVISEDAPRIL2017 www.ti.com

Electrical Characteristics (continued)

minimumandmaximumspecificationsareatT =–40°Cto+125°C,AVDD=4.75Vto5.25V;typicalspecificationsareatT

A A

=25°C;AVDD=5V,DVDD=3V,V =2.5V(internal),andf =200kSPS(unlessotherwisenoted)

REF SAMPLE

TEST

PARAMETER TESTCONDITIONS MIN TYP MAX UNIT LEVEL(1)

POWER-SUPPLYREQUIREMENTS

AVDD Analogpower-supplyvoltage Analogsupply 4.75 5 5.25 V A

DVDD Digitalpower-supplyvoltage Digitalsupplyrange 2.3 3.3 AVDD V A

ForADS8588S,AVDD=5V,

fS=200kSPS, 17.7 24.0 A

Analogsupplycurrent internalreference

IAVDD_DYN (operational) ForADS8588S,AVDD=5V, mA

fS=200kSPS, 17.1 24.0 A

externalreference

ForADS8588S,AVDD=5V,

internalreference, 12.4 17.0 A

Analogsupplycurrent devicenotconverting

IAVDD_STC (static) ForADS8588S,AVDD=5V, mA

externalreference, 12.0 17.0 A

devicenotconverting

AtAVDD=5V,deviceinSTDBY

mode, 4.2 5.5 A

AVDDsupply internalreference

IAVDD_STDBY STANDBYcurrent AtAVDD=5V,deviceinSTDBY mA

mode, 3.8 5.5 A

externalreference

AtAVDD=5V,devicein

AVDDsupply PWR_DN,internalor

IAVDD_PWR_DN power-downcurrent externalreference, 0.2 6 µA A

TA=–40°Cto+85°C

ForADS8588S,

IDVDD_DYN Digitalsupplycurrent DVDD=3.3V, 0.15 0.3 mA A

fS=200kSPS

AtAVDD=5V,deviceinSTDBY

IDVDD_STDBY DVDDsupplySTANDBYcurrent mode 0.05 1.5 µA A

AtAVDD=5V,devicein

IDVDD_PWR-DN DVDDsupplypower-downcurrent PWR_DNmode 0.05 1.5 µA A

DIGITALINPUTS(CMOS)

VIH Digitalhighinputvoltagelogiclevel DVDD>2.3V 0.7×DVDD DVDD+0.3 V A

VIL Digitallowinputvoltagelogiclevel DVDD>2.3V –0.3 0.3×DVDD V A

Inputleakagecurrent 100 nA A

Inputpincapacitance 5 pF A

DIGITALOUTPUTS(CMOS)

VOH Digitalhighoutputvoltagelogiclevel IO=100-µAsource 0.8×DVDD DVDD V A

VOL Digitallowoutputvoltagelogiclevel IO=100-µAsink 0 0.2×DVDD V A

Floatingstateleakagecurrent OnlyforSDO 1 µA A

Internalpincapacitance 5 pF A

TEMPERATURERANGE

TA Operatingfree-airtemperature –40 125 °C A

10 SubmitDocumentationFeedback Copyright©2016–2017,TexasInstrumentsIncorporated

ProductFolderLinks:ADS8588S

Description:SAR. ADC. SER/PAR. Interface. Copyright © 2017, Texas Instruments Incorporated A flexible digital interface supporting serial, parallel, and parallel Setup time: BUSY falling edge to CS falling edge, start of data read operation.