Table Of ContentLTC2208

16-Bit, 130Msps ADC

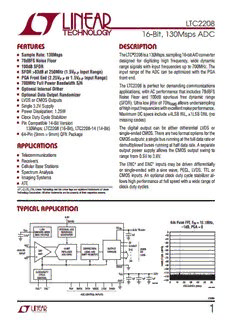

FEATURES D ESCRIPTION

n Sample Rate: 130Msps The LTC®2208 is a 130Msps, sampling 16-bit A/D converter

n 78dBFS Noise Floor designed for digitizing high frequency, wide dynamic

n 100dB SFDR range signals with input frequencies up to 700MHz. The

n SFDR >83dB at 250MHz (1.5V Input Range) input range of the ADC can be optimized with the PGA

P-P

n PGA Front End (2.25V or 1.5V Input Range) front end.

P-P P-P

n 700MHz Full Power Bandwidth S/H

The LTC2208 is perfect for demanding communications

n Optional Internal Dither

applications, with AC performance that includes 78dBFS

n Optional Data Output Randomizer

Noise Floor and 100dB spurious free dynamic range

n LVDS or CMOS Outputs

(SFDR). Ultra low jitter of 70fs allows undersampling

RMS

n Single 3.3V Supply

of high input frequencies with excellent noise performance.

n Power Dissipation: 1.25W

Maximum DC specs include ±4LSB INL, ±1LSB DNL (no

n Clock Duty Cycle Stabilizer

missing codes).

n Pin Compatible 14-Bit Version

130Msps: LTC2208 (16-Bit), LTC2208-14 (14-Bit) The digital output can be either differential LVDS or

n 64-Pin (9mm × 9mm) QFN Package single-ended CMOS. There are two format options for the

CMOS outputs: a single bus running at the full data rate or

APPLICATIONS demultiplexed buses running at half data rate. A separate

output power supply allows the CMOS output swing to

n Telecommunications range from 0.5V to 3.6V.

n Receivers

The ENC+ and ENC– inputs may be driven differentially

n Cellular Base Stations

or single-ended with a sine wave, PECL, LVDS, TTL or

n Spectrum Analysis

CMOS inputs. An optional clock duty cycle stabilizer al-

n Imaging Systems

lows high performance at full speed with a wide range of

n ATE

clock duty cycles.

L, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear

Technology Corporation. All other trademarks are the property of their respective owners.

TYPICAL APPLICATION

3.3V

SENSE 64k Point FFT, F = 15.1MHz,

IN

–1dB, PGA = 0

VCM COMM1.O2N5V MODE INRTEEFRENRAELN ACDEC OVDD 0.5V TO 3.6V 0

2.2μF BIAS VOLTAGE GENERATOR 1μF –10

–20

OF –30

ANINALPOUGTAAIINN+– –+ASM/HP PAIDP1C6E -LCBIONITREDE SHCLIOFOTRG RRIECEC GATINSIODTNER DORUITVPEURTS DCL1•••K5OUT COLVMRDOSS TUDE (dBFS) ––––45670000

D0 PLI –80

M

A –90

OGND

–100

CLOCK/DUTY –110

CYCLE VDD 3.3V

–120

CONTROL 1μF 1μF 1μF

GND –130

2208TA01 0 10 20 30 40 50 60

FREQUENCY (MHz)

ENC+ ENC– PGA SHDN DITH MODE LVDS RAND 2208 TA01b

ADC CONTROL INPUTS

2208fc

1

LTC2208

ABSOLUTE MAXIMUM RATINGS PIN CONFIGURATION

OV = V (Notes 1 and 2)

DD DD

TOP VIEW

Supply Voltage (V ) ...................................–0.3V to 4V

DAnigailtoagl OInuptpuut tV GorltoaDugDned ( NVoolttea g3)e . .(.O..G.–N0D.3) V... .t.o.. .(–VD0D.3 +V 0to.3 1VV) 64 PGA63 RAND62 MODE61 LVDS+60 OF/OFA–59 OF/DA15+58 D15/DA14–57 D15/DA13+56 D14/DA12–55 D14/DA11+54 D13/DA10–53 D13/DA9+52 D12/DA8–51 D12/DA750 OGND49 OVDD

Digital Input Voltage.....................–0.3V to (V + 0.3V)

DD SENSE1 48 D11+/DA6

Digital Output Voltage ................–0.3V to (OV + 0.3V) GND 2 47 D11–/DA5

DD VCM 3 46 D10+/DA4

Power Dissipation ............................................2000mW GND 4 45 D10–/DA3

VDD 5 44 D9+/DA2

Operating Temperature Range VDD 6 43 D9–/DA1

GND 7 42 D8+/DA0

LLTTCC22220088IC . .........................................................................................–..4.00°°CC ttoo 8705°°CC GAANIIDNN +–1 890 65 344910 CDCLL8KK–/OOCUULTTK+O–//CUOLTFKABOUTB

GND 11 38 D7+/DB15

Storage Temperature Range ..................–65°C to 150°C ENC+ 12 37 D7–/DB14

Digital Output Supply Voltage (OV ) ..........–0.3V to 4V ENC– 13 36 D6+/DB13

DD GND 14 35 D6–/DB12

VDD 15 34 D5+/DB11

VDD 16 33 D5–/DB10

V 17DDGND 18SHDN19DITH20–D0/DB0 21+DO/DB1 22–D1/DB2 23+D1/DB3 24–D2/DB4 25+D2/DB5 26–D3/DB6 27+D3/DB7 28–D4/DB8 29+ D4/DB9 30 OGND 31 OV 32DD

UP PACKAGE

64-LEAD (9mm (cid:115) 9mm) PLASTIC QFN

TJMAX = 150°C, θJA = 20°C/W

EXPOSED PAD (PIN 65) IS GND, MUST BE SOLDERED TO PCB

ORDER INFORMATION

LEAD FREE FINISH TAPE AND REEL PART MARKING* PACKAGE DESCRIPTION TEMPERATURE RANGE

LTC2208CUP#PBF LTC2208CUP#TRPBF LTC2208UP 64-Lead (9mm × 9mm) Plastic QFN 0°C to 70°C

LTC2208IUP#PBF LTC2208IUP#TRPBF LTC2208UP 64-Lead (9mm × 9mm) Plastic QFN –40°C to 85°C

Consult LTC Marketing for parts specifi ed with wider operating temperature ranges. *The temperature grade is identifi ed by a label on the shipping container

Consult LTC Marketing for information on non-standard lead based fi nish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifi cations, go to: http://www.linear.com/tapeandreel/

CONVERTER CHARACTERISTICS

The l denotes the specifi cations which apply over the full operating

temperature range, otherwise specifi cations are at T = 25°C. (Note 4)

A

PARAMETER CONDITIONS MIN TYP MAX UNITS

Integral Linearity Error Differential Analog Input (Note 5) T = 25°C ±1.2 ±4.0 LSB

A

Integral Linearity Error Differential Analog Input (Note 5) l ±1.5 ±4.5 LSB

Differential Linearity Error Differential Analog Input l ±0.3 ±1 LSB

Offset Error (Note 6) l ±2 ±8.5 mV

Offset Drift ±10 μV/°C

Gain Error External Reference l ±0.2 ±1.5 %FS

Full-Scale Drift Internal Reference ±30 ppm/°C

External Reference ±15 ppm/°C

Transition Noise External Reference 2.9 LSB

RMS

2208fc

2

LTC2208

ANALOG INPUT

The l denotes the specifi cations which apply over the full operating temperature range, otherwise

specifi cations are at T = 25°C. (Note 4)

A

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

VIN Analog Input Range (AIN+ – AIN–) 3.135V ≤ VDD ≤ 3.465V 1.5 or 2.25 VP-P

V Analog Input Common Mode Differential Input (Note 7) l 1 1.25 1.5 V

IN, CM

IIN Analog Input Leakage Current 0V ≤ AIN+, AIN– ≤ VDD l –1 1 μA

I SENSE Input Leakage Current 0V ≤ SENSE ≤ V l –3 3 μA

SENSE DD

I MODE Pin Pull-Down Current to GND 10 μA

MODE

I LVDS Pin Pull-Down Current to GND 10 μA

LVDS

C Analog Input Capacitance Sample Mode ENC+ < ENC– 6.5 pF

IN

Hold Mode ENC+ > ENC– 1.8 pF

t Sample-and-Hold 1 ns

AP

Acquisition Delay Time

t Sample-and-Hold 70 fs RMS

JITTER

Acquisition Delay Time Jitter

CMRR Analog Input 1V < (A + = A –) <1.5V 80 dB

IN IN

Common Mode Rejection Ratio

BW-3dB Full Power Bandwidth R < 25Ω 700 MHz

S

DYNAMIC ACCURACY

The l denotes the specifi cations which apply over the full operating temperature range,

otherwise specifi cations are at T = 25°C. A = –1dBFS. (Note 4)

A IN

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

SNR Signal-to-Noise Ratio 5MHz Input (2.25V Range, PGA = 0) 77.7 dBFS

5MHz Input (1.5V Range, PGA = 1) 75.3 dBFS

30MHz Input (2.25V Range, PGA = 0) T = 25°C 76.5 77.6 dBFS

A

30MHz Input (2.25V Range, PGA = 0) l 76.1 77.3 dBFS

30MHz Input (1.5V Range, PGA = 1) 75.2 dBFS

70MHz Input (2.25V Range, PGA = 0) 77.5 dBFS

70MHz Input (1.5V Range, PGA = 1) 75.1 dBFS

140MHz Input (2.25V Range, PGA = 0) 76.9 dBFS

140MHz Input (1.5V Range, PGA = 1) T = 25°C 73.8 74.8 dBFS

A

140MHz Input (1.5V Range, PGA = 1) l 73.4 74.5 dBFS

250MHz Input (2.25V Range, PGA = 0) 75.4 dBFS

250MHz Input (1.5V Range, PGA =1) 73.8 dBFS

SFDR Spurious Free 5MHz Input (2.25V Range, PGA = 0) 100 dBc

Dynamic Range 5MHz Input (1.5V Range, PGA = 1) 100 dBc

2nd or 3rd Harmonic

30MHz Input (2.25V Range, PGA = 0) T = 25°C 88 95 dBc

A

30MHz Input (2.25V Range, PGA = 0) l 87 94 dBc

30MHz Input (1.5V Range, PGA = 1) 100 dBc

70MHz Input (2.25V Range, PGA = 0) 90 dBc

70MHz Input (1.5V Range, PGA = 1) 95 dBc

140MHz Input (2.25V Range, PGA = 0) 85 dBc

140MHz Input (1.5V Range, PGA = 1) T = 25°C 86 90 dBc

A

140MHz Input (1.5V Range, PGA = 1) l 84 89 dBc

250MHz Input (2.25V Range, PGA = 0) 78 dBc

250MHz Input (1.5V Range, PGA = 1) 83 dBc

2208fc

3

LTC2208

DYNAMIC ACCURACY

The l denotes the specifi cations which apply over the full operating temperature range,

otherwise specifi cations are at T = 25°C. A = –1dBFS unless otherwise noted. (Note 4)

A IN

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

SFDR Spurious Free 5MHz Input (2.25V Range, PGA = 0) 100 dBc

Dynamic Range 5MHz Input (1.5V Range, PGA = 1) 100 dBc

4th Harmonic 30MHz Input (2.25V Range, PGA = 0) l 90 100 dBc

or Higher

30MHz Input (1.5V Range, PGA = 1) 100 dBc

70MHz Input (2.25V Range, PGA = 0) 100 dBc

70MHz Input (1.5V Range, PGA = 1) 100 dBc

140MHz Input (2.25V Range, PGA = 0) 95 dBc

140MHz Input (1.5V Range, PGA = 1) l 88 95 dBc

250MHz Input (2.25V Range, PGA = 0) 90 dBc

250MHz Input (1.5V Range, PGA = 1) 90 dBc

S/(N+D) Signal-to-Noise 5MHz Input (2.25V Range, PGA = 0) 77.7 dBFS

Plus Distortion Ratio 5MHz Input (1.5V Range, PGA = 1) 75.3 dBFS

30MHz Input (2.25V Range, PGA = 0) T = 25°C 76.3 77.5 dBFS

A

30MHz Input (2.25V Range, PGA = 0) l 75.9 77.5 dBFS

30MHz Input (1.5V Range, PGA = 1) 75.2 dBFS

70MHz Input (2.25V Range, PGA = 0) 77.4 dBFS

70MHz Input (1.5V Range, PGA = 1) 75 dBFS

140MHz Input (2.25V Range, PGA = 0) 76.4 dBFS

140MHz Input (1.5V Range, PGA = 1) T = 25°C 73.6 74.5 dBFS

A

140MHz Input (1.5V Range, PGA = 1) l 73.2 74.5 dBFS

250MHz Input (2.25V Range, PGA = 0) 73.6 dBFS

250MHz Input (1.5V Range, PGA = 1) 72.9 dBFS

SFDR Spurious Free Dynamic Range 5MHz Input (2.25V Range, PGA = 0) 105 dBFS

at –25dBFS 5MHz Input (1.5V Range, PGA = 1) 105 dBFS

Dither “OFF”

30MHz Input (2.25V Range, PGA = 0) 105 dBFS

30MHz Input (1.5V Range, PGA = 1) 105 dBFS

70MHz Input (2.25V Range, PGA = 0) 105 dBFS

70MHz Input (1.5V Range, PGA = 1) 105 dBFS

14 0MHz Input (2.25V Range, PGA = 0) 100 dBFS

140MHz Input (1.5V Range, PGA = 1) 100 dBFS

250MHz Input (2.25V Range, PGA = 0) 100 dBFS

250MHz Input (1.5V Range, PGA = 1) 100 dBFS

SFDR Spurious Free Dynamic Range 5MHz Input (2.25V Range, PGA = 0) 115 dBFS

at –25dBFS 5MHz Input (1.5V Range, PGA = 1) 115 dBFS

Dither “ON” 30MHz Input (2.25V Range, PGA = 0) l 100 115 dBFS

30MHz Input (1.5V Range, PGA = 1) 115 dBFS

70MHz Input (2.25V Range, PGA = 0) 115 dBFS

70MHz Input (1.5V Range, PGA = 1) 115 dBFS

140MHz Input (2.25V Range, PGA = 0) 110 dBFS

140MHz Input (1.5V Range, PGA = 1) 110 dBFS

250MHz Input (2.25V Range, PGA = 0) 105 dBFS

250MHz Input (1.5V Range, PGA = 1) 105 dBFS

2208fc

4

LTC2208

COMMON MODE BIAS CHARACTERISTICS

The l denotes the specifi cations which apply over

the full operating temperature range, otherwise specifi cations are at T = 25°C. (Note 4)

A

PARAMETER CONDITIONS MIN TYP MAX UNITS

V Output Voltage I = 0 1.15 1.25 1.35 V

CM OUT

V Output Tempco I = 0 +40 ppm/°C

CM OUT

V Line Regulation 3.135V ≤ V ≤ 3.465V 1 mV/ V

CM DD

V Output Resistance 1mA ≤ | I | ≤ 1mA 2 Ω

CM OUT

DIGITAL INPUTS AND DIGITAL OUTPUTS

The l denotes the specifi cations which apply over the

full operating temperature range, otherwise specifi cations are at T = 25°C. (Note 4)

A

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

ENCODE INPUTS (ENC+, ENC–)

V Differential Input Voltage (Note 7) l 0.2 V

ID

V Common Mode Input Voltage Internally Set 1.6 V

ICM

Externally Set (Note 7) 1.2 3.0 V

RIN Input Resistance (See Figure 2) 6 kΩ

C Input Capacitance (Note 7) 3 pF

IN

LOGIC INPUTS (DITH, PGA, SHDN, RAND)

V High Level Input Voltage V = 3.3V l 2 V

IH DD

V Low Level Input Voltage V = 3.3V l 0.8 V

IL DD

I Digital Input Current V = 0V to V l ±10 μA

IN IN DD

C Digital Input Capacitance (Note 7) 1.5 pF

IN

LOGIC OUTPUTS (CMOS MODE)

OV = 3.3V

DD

V High Level Output Voltage V = 3.3V I = –10μA 3.299 V

OH DD O

I = –200μA l 3.1 3.29 V

O

V Low Level Output Voltage V = 3.3V I = 160μA 0.01 V

OL DD O

I = 1.6mA l 0.10 0.4 V

O

I Output Source Current V = 0V –50 mA

SOURCE OUT

I Output Sink Current V = 3.3V 50 mA

SINK OUT

OV = 2.5V

DD

V High Level Output Voltage V = 3.3V I = –200μA 2.49 V

OH DD O

V Low Level Output Voltage V = 3.3V I = 1.60mA 0.1 V

OL DD O

OV = 1.8V

DD

V High Level Output Voltage V = 3.3V I = –200μA 1.79 V

OH DD O

V Low Level Output Voltage V = 3.3V I = 1.60mA 0.1 V

OL DD O

LOGIC OUTPUTS (LVDS MODE)

STANDARD LVDS

VOD Differential Output Voltage 100Ω Differential Load l 247 350 454 mV

VOS Output Common Mode Voltage 100Ω Differential Load l 1.125 1.2 1.375 V

LOW POWER LVDS

VOD Differential Ouptut Voltage 100Ω Differential Load l 125 175 250 mV

VOS Output Common Mode Voltage 100Ω Differential Load l 1.125 1.2 1.375 V

2208fc

5

LTC2208

POWER REQUIREMENTS

The l denotes the specifi cations which apply over the full operating temperature

range, otherwise specifi cations are at T = 25°C. A = –1dBFS. (Note 4)

A IN

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V Analog Supply Voltage (Note 8) l 3.135 3.3 3.465 V

DD

P Shutdown Power SHDN = V 0.2 mW

SHDN DD

STANDARD LVDS OUTPUT MODE

OV Output Supply Voltage (Note 8) l 3 3.3 3.6 V

DD

I Analog Supply Current l 380 450 mA

VDD

I Output Supply Current l 74 90 mA

OVDD

P Power Dissipation l 1498 1782 mW

DIS

LOW POWER LVDS OUTPUT MODE

OV Output Supply Voltage (Note 8) l 3 3.3 3.6 V

DD

I Analog Supply Current l 380 450 mA

VDD

I Output Supply Current l 31 50 mA

OVDD

P Power Dissipation l 1356 1650 mW

DIS

CMOS OUTPUT MODE

OV Output Supply Voltage (Note 8) l 0.5 3.6 V

DD

I Analog Supply Current l 380 450 mA

VDD

P Power Dissipation l 1250 1485 mW

DIS

TIMING CHARACTERISTICS

The l denotes the specifi cations which apply over the full operating temperature

range, otherwise specifi cations are at T = 25°C. (Note 4)

A

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

f Sampling Frequency (Note 8) l 1 130 MHz

S

t ENC Low Time Duty Cycle Stabilizer Off (Note 7) l 3.65 3.846 1000 ns

L

Duty Cycle Stabilizer On (Note 7) l 2.6 3.846 1000 ns

t ENC High Time Duty Cycle Stabilizer Off (Note 7) l 3.65 3.846 1000 ns

H

Duty Cycle Stabilizer On (Note 7) l 2.6 3.846 1000 ns

t Sample-and-Hold Aperture Delay –1 ns

AP

LVDS OUTPUT MODE (STANDARD and LOW POWER)

t ENC to DATA Delay (Note 7) l 1.3 2.5 3.8 ns

D

t ENC to CLKOUT Delay (Note 7) l 1.3 2.5 3.8 ns

C

t DATA to CLKOUT Skew (t -t ) (Note 7) l –0.6 0 0.6 ns

SKEW C D

t Output Rise Time 0.5 ns

RISE

t Output Fall Time 0.5 ns

FALL

Data Latency Data Latency 7 Cycles

CMOS OUTPUT MODE

t ENC to DATA Delay (Note 7) l 1.3 2.7 4.0 ns

D

t ENC to CLKOUT Delay (Note 7) l 1.3 2.7 4.0 ns

C

t DATA to CLKOUT Skew (t -t ) (Note 7) l –0.6 0 0.6 ns

SKEW C D

Data Latency Data Latency Full Rate CMOS 7 Cycles

Demuxed 7 Cycles

2208fc

6

LTC2208

ELECTRICAL CHARACTERISTICS

Note 1: Stresses beyond those listed under Absolute Maximum Ratings Note 5: Integral nonlinearity is defi ned as the deviation of a code from a “best

may cause permanent damage to the device. Exposure to any Absolute fi t straight line” to the transfer curve. The deviation is measured from the

Maximum Rating condition for extended periods may affect device center of the quantization band.

reliability and lifetime. Note 6: Offset error is the offset voltage measured from –1/2LSB when the

Note 2: All voltage values are with respect to GND, with GND and OGND output code fl ickers between 0000 0000 0000 0000 and 1111 1111 1111

shorted (unless otherwise noted). 1111 in 2’s complement output mode.

Note 3: When these pin voltages are taken below GND or above VDD, they Note 7: Guaranteed by design, not subject to test.

will be clamped by internal diodes. This product can handle input currents Note 8: Recommended operating conditions.

of greater than 100mA below GND or above V without latchup.

DD

Note 4: V = 3.3V, f = 130MHz, LVDS outputs, differential ENC+/

DD SAMPLE

ENC– = 2V sine wave with 1.6V common mode, input range = 2.25V

P-P P-P

with differential drive (PGA = 0), unless otherwise specifi ed.

TIMING DIAGRAMS

LVDS Output Mode Timing

All Outputs are Differential and Have LVDS Levels

tAP

N + 1 N + 4

ANALOG

INPUT N N + 3

N + 2

tH

tL

ENC–

ENC+

tD

D0-D15, OF N – 7 N – 6 N – 5 N – 4 N – 3

tC

CLKOUT+

CLKOUT– 2208 TD01

2208fc

7

LTC2208

TIMING DIAGRAMS

Full-Rate CMOS Output Mode Timing

All Outputs are Single-Ended and Have CMOS Levels

tAP

N + 1 N + 4

ANALOG

INPUT N N + 3

N + 2

tH

tL

ENC–

ENC+

tD

DA0-DA15, OFA N – 7 N – 6 N – 5 N – 4 N – 3

tC

CLKOUTA

CLKOUTB

DB0-DB15, OFB HIGH IMPEDANCE

2208 TD02

Demultiplexed CMOS Output Mode Timing

All Outputs are Single-Ended and Have CMOS Levels

tAP

N + 1 N + 4

ANALOG

INPUT N N + 3

N + 2

tH

tL

ENC–

ENC+

tD

DA0-DA15, OFA N – 8 N – 6 N – 4

tD

DB0-DB15, OFB N – 7 N – 5 N – 3

tC

CLKOUTA

CLKOUTB 2208 TD03

2208fc

8

LTC2208

TYPICAL PERFORMANCE CHARACTERISTICS

Integral Nonlinearity (INL) vs Differential Nonlinearity (DNL) vs

Output Code Output Code AC Grounded Input Histogram

2 1 10000

0.8 9000

1.5

0.6 8000

1

B) B) 0.4 7000

NL ERROR (LS–00..055 NL ERROR (LS 00..220 COUNT465000000000

I D 0.4 3000

–1

0.6 2000

–1.5 0.8 1000

–2 1 0

0 16384 32768 49152 65536 0 16384 32768 49152 65536 32736 32740 32744 32748 32752 32756

OUTPUT CODE OUTPUT CODE OUTPUT CODE

2208 G01 2208 G02 2208 G14

128k Point FFT, f = 4.93MHz, 64k Point FFT, f = 15.1MHz, 64k Point FFT, 15.1MHz, –20dBFS,

IN IN

–1dBFS, PGA = 0 –1dBFS, PGA = 0 PGA = 0, Internal Dither “Off”

0 0 0

–10 –10 –10

–20 –20 –20

–30 –30 –30

S) –40 S) –40 S) –40

BF –50 BF –50 BF –50

DE (d –60 DE (d –60 DE (d –60

PLITU ––8700 PLITU ––7800 PLITU ––7800

M M M

A –90 A –90 A –90

–100 –100 –100

–110 –110 –110

–120 –120 –120

–130 –130 –130

0 10 20 30 40 50 60 0 10 20 30 40 50 60 0 10 20 30 40 50 60

FREQUENCY (MHz) FREQUENCY (MHz) FREQUENCY (MHz)

2208 G15 2208 G03 2208 G04

32k Point 2-Tone FFT, 32k Point 2-Tone FFT,

64k Point FFT, 15.1MHz, –20dBFS, f = 21.14MHz and 14.25MHz, f = 20.14MHz and 14.25MHz,

IN IN

PGA = 0, Internal Dither “On” –7dBFS, PGA = 0 –25dBFS, PGA = 0

0 0 0

–10 –10 –10

–20 –20 –20

–30 –30 –30

S) –40 S) –40 S) –40

F F F

B –50 B B

d d –50 d –50

E ( –60 E ( E (

D D –60 D –60

U –70 U U

PLIT –80 PLIT –70 PLIT –70

M M –80 M –80

A –90 A A

–100 –90 –90

–110 –100 –100

–120 –110 –110

–130 –120 –120

0 10 20 30 40 50 60 0 10 20 30 40 50 60 0 10 20 30 40 50 60

FREQUENCY (MHz) FREQUENCY (MHz) FREQUENCY (MHz)

2208 G05 2208 G06 2208 G07

2208fc

9

LTC2208

TYPICAL PERFORMANCE CHARACTERISTICS

SFDR vs Input Level, fIN = 15MHz, SFDR vs Input Level, fIN = 15MHz, 64k Point FFT, fIN = 30.1MHz,

PGA = 0, Dither “Off” PGA = 0, Dither “On” –1dBFS, PGA = 0

140 140 0

130 130 –10

120 120 –20

110 110 –30

SFDR (dBc AND dBFS)186497500000000 SFDR (dBc AND dBFS)186497500000000 AMPLITUDE (dBFS) ––––––896457000000

30 30 –100

20 20 –110

10 10 –120

0 0 –130

–80 –70 –60 –50 –40 –30 –20 –10 0 –80 –70 –60 –50 –40 –30 –20 –10 0 0 10 20 30 40 50 60

INPUT LEVEL (dBFS) INPUT LEVEL (dBFS) FREQUENCY (MHz)

2208 G08 2208 G09 2208 G16

128k Point FFT, fIN = 30.1MHz, 64k Point FFT, fIN = 70.1MHz, 64k Point FFT, fIN = 70.1MHz,

–25dBFS, PGA = 0, Dither “On” –1dBFS, PGA = 0 –10dBFS, PGA = 0

0 0 0

–10 –10 –10

–20 –20 –20

–30 –30 –30

S) –40 S) –40 S) –40

F F F

B –50 B –50 B –50

d d d

E ( –60 E ( –60 E ( –60

D D D

TU –70 TU –70 TU –70

PLI –80 PLI –80 PLI –80

M M M

A –90 A –90 A –90

–100 –100 –100

–110 –110 –110

–120 –120 –120

–130 –130 –130

0 10 20 30 40 50 60 0 10 20 30 40 50 60 0 10 20 30 40 50 60

FREQUENCY (MHz) FREQUENCY (MHz) FREQUENCY (MHz)

2208 G17 2208 G18 2208 G19

64k Point FFT, fIN = 70.1MHz, 128k Point FFT, fIN = 70.1MHz, 64k Point FFT, fIN = 70.1MHz,

–20dBFS, PGA = 0 –25dBFS, PGA = 0, Dither “On” –1dBFS, PGA = 1

0 0 0

–10 –10 –10

–20 –20 –20

–30 –30 –30

S) –40 S) –40 S) –40

BF –50 BF –50 BF –50

DE (d –60 DE (d –60 DE (d –60

PLITU ––8700 PLITU ––8700 PLITU ––8700

M M M

A –90 A –90 A –90

–100 –100 –100

–110 –110 –110

–120 –120 –120

–130 –130 –130

0 10 20 30 40 50 60 0 10 20 30 40 50 60 0 10 20 30 40 50 60

FREQUENCY (MHz) FREQUENCY (MHz) FREQUENCY (MHz)

2208 G20 2208 G21 2208 G22

2208fc

10

Description:input range of the ADC can be optimized with the PGA front end ADC

CONTROL INPUTS. AIN+ Refer to Internal Dither section of this data sheet for

details.