Programming Model Appendices LonTalk Protocol Electrical and Mechanical Specifications Input ... PDF

Preview Programming Model Appendices LonTalk Protocol Electrical and Mechanical Specifications Input ...

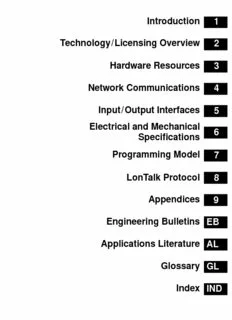

Introduction 1 Technology/Licensing Overview 2 Hardware Resources 3 Network Communications 4 Input/Output Interfaces 5 Electrical and Mechanical 6 Specifications Programming Model 7 LonTalk Protocol 8 Appendices 9 Engineering Bulletins EB Applications Literature AL Glossary GL Index IND DATA CLASSIFICATION Product Preview This heading on a data sheet indicates that the device is in the formative stages or under development at the time of printing of this data book. Please check with Motorola for current status. The disclaimer at the bottom of the first page reads: “This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.” Advance Information This heading on a data sheet indicates that the device is in sampling, preproduction, or first production stages at the time of printing of this data book. Please check with Motorola for updated information. The disclaimer at the bottom of the first page reads: “This document contains information on a new product. Specifications and information herein are subject to change without notice.” Fully Released A fully released data sheet contains neither a classification heading nor a disclaimer at the bottom of the first page. This document contains information on a product in full production. Guaranteed limits will not be changed without written notice to your local Motorola Semiconductor Sales Office. Technical Summary The Technical Summary is an abridged version of the complete device data sheet that contains the key technical information required to determine the correct device for a specific application. Complete device data sheets for these more complex devices are available from your Motorola Semiconductor Sales Office or authorized distributor. L W ON ORKS Technology Device Data, Rev. 5 Volume III — Applications Literature Through the LONWORKS program, Motorola offers the MC143120 and MC143150 Neuron integrated circuits. These integrated circuits are sophisticated VLSI devices for network applications. The LONWORKS Technology Device Data Book combines specifications on these parts with a large selection of applications literature. The applications literature is included in this book in order to provide you with suggestions and hints for implementing network solutions in your own applications. This book is divided into three volumes: • Volume I — Device Data • Volume II — Engineering Bulletins from Echelon • Volume III — Applications Literature For the most current copy of this data book, please visit our web site at: http://motorola.com/lonworks Increasingly sophisticated LONWORKS devices are constantly under development. For the latest releases, additional technical information, and pricing, please contact your nearest Motorola Semiconductor Sales Office or authorized distributor. A complete listing of sales offices and distributors is included at the back of this book. Motorola LONWORKS Application Support Austin, Texas: (512) 934-7610 FAX: (512) 934-7991 http://motorola.com/lonworks Toulouse, France: 33-561-199175 Hong Kong: 852-2-666-8470 Tokyo, Japan: 81-33-280-8414 Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters can and do vary in different applications. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer. ª Motorola, Inc. 1998 Previous Edition ª 1998 “All Rights Reserved” This IC contains firmware which has license restrictions. Sample Neurons can be obtained from Motorola after signing a developers license agreement with Echelon Corporation. Production procurement of the Neuron Chips can be acquired from Motorola only after signing an OEM license agreement with Echelon Corporation. Echelon, LON, LonBuilder, LonManager, LonTalk, LonUsers, LONWORKS, Neuron, 3120, 3150, and NodeBuilder are regis- tered trademarks of Echelon Corporation. LonLink, LonMaker, LONMARK, LONews, and LonSupport are trademarks of Echelon Corporation. SIDACtor is a trademark of Teccor Electronics, Inc. CONTENTS SECTION 1 INTRODUCTION 1–3 (I) SECTION 2 LONWORKS TECHNOLOGY AND LICENSING OVERVIEW 2–3 (I) 2.1 LONWORKS TECHNOLOGY OVERVIEW AND ARCHITECTURE. . . . . . . . . . . . . . . . . .2–3 (I) MC143120B1DW Neuron Chip Distributed Communications and Control Processor . . . . . . .2–5 (I) MC143120E2 Neuron Chip Distributed Communications and Control Processor . . . . . . .2–6 (I) MC143120FE2 Neuron Chip Distributed Communications and Control Processor . . . . . . .2–8 (I) MC143120LE2 Neuron Chip Distributed Communications and Control Processor . . . . . .2–10 (I) MC143150B1FU1 Neuron Chip Distributed Communications and Control Processor . . . . . .2–12 (I) MC143150B2 Neuron Chip Distributed Communications and Control Processor . . . . . .2–13 (I) SECTION 3 Neuron CHIP PROCESSOR FAMILY — HARDWARE RESOURCES 3–3 (I) 3.1 PROCESSING UNITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–3 (I) 3.2 MEMORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–9 (I) 3.2.1 Memory Allocation Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–9 (I) 3.2.2 EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–9 (I) 3.2.3 Static RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–12 (I) 3.2.4 Preprogrammed ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–12 (I) 3.2.5 External Memory (MC143150 Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–12 (I) 3.2.6 Memory Integrity Using Checksums. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–13 (I) 3.3 INPUT/OUTPUT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–16 (I) 3.3.1 Eleven Bidirectional I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–16 (I) 3.3.2 Two 16-Bit Timer/Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3–16 (I) SECTION 4 COMMUNICATIONS, CLOCKING, RESET, AND SERVICE 4–3 (I) 4.1 COMMUNICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–3 (I) 4.2 COMMUNICATIONS PORT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–4 (I) 4.2.1 Single-Ended Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–5 (I) 4.2.2 Differential Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–8 (I) 4.2.3 Special-Purpose Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–9 (I) 4.3 TWISTED-PAIR TRANSCEIVERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–12 (I) 4.3.1 Direct-Drive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–12 (I) 4.3.2 EIA-485 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–13 (I) 4.3.3 Transformer-Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–14 (I) 4.4 OTHER TRANSCEIVER EXAMPLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–17 (I) 4.4.1 Powerline Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–17 (I) 4.4.2 Radio Frequency Transceivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–17 (I) 4.5 CLOCKING SYSTEM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–17 (I) 4.5.1 Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–17 (I) 4.6 ADDITIONAL FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–19 (I) 4.6.1 Sleep/Wake-Up Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–19 (I) 4.6.2 Reset Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–20 (I) 4.6.3 RESET Pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–21 (I) 4.6.4 Reset Processes and Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–23 (I) 4.7 SERVICE PIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4–30 (I) MOTOROLA LONWORKS TECHNOLOGY TABLE OF CONTENTS v CONTENTS (CONTINUED) SECTION 5 INPUT/OUTPUT INTERFACES 5–3 (I) 5.1 HARDWARE CONSIDERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–4 (I) 5.2 I/O TIMING ISSUES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–8 (I) 5.2.1 Scheduler-Related I/O Timing Information. . . . . . . . . . . . . . . . . . . . . . . . . . . .5–8 (I) 5.2.2 Firmware and Hardware Related I/O Timing Information. . . . . . . . . . . . . . . .5–10 (I) 5.3 DIRECT OBJECTS (BIT I/O, BYTE I/O, LEVELDETECT, AND NIBBLE). . . . . . . . . . .5–10 (I) 5.3.1 Bit I/O. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–10 (I) 5.3.2 Byte I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–12 (I) 5.3.3 Leveldetect (Logic Low Level for Input > 200 ns). . . . . . . . . . . . . . . . . . . . . .5–13 (I) 5.3.4 Nibble I/O. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–13 (I) 5.4 PARALLEL I/O INTERFACE OBJECT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–15 (I) 5.4.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–15 (I) 5.4.2 Master/Slave A Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–15 (I) 5.4.3 Slave B Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–19 (I) 5.4.4 Token Passing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–20 (I) 5.4.5 Handshaking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–20 (I) 5.4.6 Data Transferring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–22 (I) 5.5 SERIAL OBJECTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–24 (I) 5.5.1 Bitshift I/O. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–24 (I) 5.5.2 I2C I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–26 (I) 5.5.3 Magcard Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–28 (I) 5.5.4 Magtrack1 Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–29 (I) 5.5.5 Neurowire (SPI Interface) I/O Object . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–30 (I) 5.5.6 Serial I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–33 (I) 5.5.7 Touch I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–34 (I) 5.5.8 Wiegand Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–36 (I) 5.6 TIMER/COUNTER OBJECTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–37 (I) 5.6.1 Timer/Counter Input Objects (Dualslope, Edgelog, Infrared, Ontime, Period, Pulsecount Input, Quadrature, Totalcount) . . . . . . . . . . . . .5–38 (I) 5.6.2 Timer/Counter Output Objects (Edgedivide, Frequency, Oneshot, Pulsecount Output, Pulsewidth, Triac, Triggered Count). . . . . . . . . . . . . . . .5–47 (I) 5.7 MUXBUS I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–55 (I) 5.8 NOTES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5–56 (I) SECTION 6 Neuron CHIP ELECTRICAL AND MECHANICAL SPECIFICATIONS 6–3 (I) 6.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–3 (I) 6.2 ELECTRICAL SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–4 (I) 6.2.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–4 (I) 6.2.2 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–4 (I) 6.2.3 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–5 (I) 6.2.4 External Memory Interface Timing — MC143150B1/B2, V – 10% . . . . . .6–11 (I) DD 6.2.5 Communications Port Programmable Hysteresis Values. . . . . . . . . . . . . . . .6–14 (I) 6.2.6 Communications Port Programmable Glitch Filter Values. . . . . . . . . . . . . . .6–14 (I) 6.2.7 Receiver* (End-to-End) Absolute Asymmetry . . . . . . . . . . . . . . . . . . . . . . . .6–14 (I) 6.2.8 Differential Receiver (End-to-End) Absolute Symmetry. . . . . . . . . . . . . . . . .6–15 (I) 6.2.9 Differential Transceiver Electrical Characteristics . . . . . . . . . . . . . . . . . . . . .6–15 (I) TABLE OF CONTENTS MOTOROLA LONWORKS TECHNOLOGY vi CONTENTS (CONTINUED) 6.3 MECHANICAL SPECIFICATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–16 (I) 6.3.1 Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–16 (I) 6.3.2 MC143150 Pin Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–17 (I) 6.3.3 MC143150 Package Dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–18 (I) 6.3.4 MC143150 Pad Layout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–19 (I) 6.3.5 MC143120 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–20 (I) 6.3.6 MC143120 Package Dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–21 (I) 6.3.7 MC143120 Pad Layout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–23 (I) 6.3.8 Sockets for Neuron Chips . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–23 (I) 6.3.9 Test Clips. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6–23 (I) SECTION 7 LONWORKS PROGRAMMING MODEL 7–3 (I) 7.1 TIMERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7–3 (I) 7.2 NETWORK VARIABLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7–3 (I) 7.3 NETWORK VARIABLE ALIASES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7–6 (I) 7.4 EXPLICIT MESSAGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7–6 (I) 7.5 SCHEDULER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7–9 (I) 7.6 ADDITIONAL LIBRARY FUNCTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7–10 (I) 7.7 BUILT-IN VARIABLES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7–15 (I) 7.8 MC143120 AND MC143120E2 FIRMWARE EXTENSIONS. . . . . . . . . . . . . . . . . . . . .7–16 (I) SECTION 8 LonTalk PROTOCOL 8–3 (I) 8.1 MULTIPLE MEDIA SUPPORT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8–3 (I) 8.2 SUPPORT FOR MULTIPLE COMMUNICATION CHANNELS . . . . . . . . . . . . . . . . . . . .8–3 (I) 8.3 COMMUNICATIONS RATES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8–4 (I) 8.4 LonTalk ADDRESSING LIMITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8–4 (I) 8.5 MESSAGE SERVICES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8–5 (I) 8.6 AUTHENTICATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8–5 (I) 8.7 PRIORITY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8–6 (I) 8.8 COLLISION AVOIDANCE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8–6 (I) 8.9 COLLISION DETECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8–6 (I) 8.10 DATA INTERPRETATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8–6 (I) 8.11 NETWORK MANAGEMENT AND DIAGNOSTIC SERVICES. . . . . . . . . . . . . . . . . . . . .8–6 (I) APPENDIX A Neuron CHIP DATA STRUCTURES 9–3 (I) A.1 FIXED READ-ONLY DATA STRUCTURE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–6 (I) A.2 THE DOMAIN TABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–11 (I) A.3 THE ADDRESS TABLE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–12 (I) A.3.1 Declaration of Group Address Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–13 (I) A.3.2 Group Address Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–14 (I) A.3.3 Declaration of Subnet/Node Address Format. . . . . . . . . . . . . . . . . . . . . . . . .9–14 (I) A.3.4 Subnet/Node Address Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . .9–14 (I) A.3.5 Declaration of Broadcast Address Format. . . . . . . . . . . . . . . . . . . . . . . . . . .9–15 (I) MOTOROLA LONWORKS TECHNOLOGY TABLE OF CONTENTS vii A.3.6 Broadcast Address Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–15 (I) A.3.7 Declaration of Turnaround Address Format. . . . . . . . . . . . . . . . . . . . . . . . . .9–15 (I) A.3.8 Turnaround Address Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–15 (I) A.3.9 Declaration of Neuron ID Address Format. . . . . . . . . . . . . . . . . . . . . . . . . . .9–16 (I) A.3.10 Neuron ID Address Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–16 (I) A.3.11 Timer Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–16 (I) A.4 NETWORK VARIABLE AND ALIAS TABLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–17 (I) A.4.1 Network Variable Configuration Table Field Descriptions . . . . . . . . . . . . . . .9–19 (I) A.4.2 Network Variable Alias Table Field Descriptions . . . . . . . . . . . . . . . . . . . . . .9–20 (I) A.4.3 Network Variable Fixed Table Field Descriptions. . . . . . . . . . . . . . . . . . . . . .9–20 (I) A.5 THE STANDARD NETWORK VARIABLE TYPE STRUCTURES. . . . . . . . . . . . . . . . .9–20 (I) A.5.1 SNVT Structure Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–21 (I) A.5.2 SNVT Descriptor Table Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . .9–22 (I) A.5.3 SNVT Table Extension Records. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–23 (I) A.5.4 SNVT Alias Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–24 (I) A.6 THE CONFIGURATION STRUCTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–24 (I) A.6.1 Configuration Structure Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . .9–25 (I) A.6.2 Direct-Mode Transceiver Parameters Field Descriptions. . . . . . . . . . . . . . . .9–28 (I) APPENDIX B NETWORK MANAGEMENT AND DIAGNOSTIC SERVICES 9–30 (I) B.1 NETWORK MANAGEMENT MESSAGES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–35 (I) B.1.1 Node Identification Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–35 (I) B.1.2 Domain Table Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–36 (I) B.1.3 Address Table Messages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–38 (I) B.1.4 Network Variable-Related Messages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–39 (I) B.1.5 Memory-Related Messages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–42 (I) B.1.6 Special-Purpose Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–47 (I) B.2 NETWORK DIAGNOSTIC MESSAGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–50 (I) B.3 NETWORK VARIABLE MESSAGES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–53 (I) APPENDIX C EXTERNAL MEMORY INTERFACING 9–57 (I) APPENDIX D DESIGN AND HANDLING GUIDELINES 9–63 (I) D.1 APPLICATION CONSIDERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–63 (I) D.1.1 Termination of Unused Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–63 (I) D.1.2 Avoidance of Damaging Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–64 (I) D.1.3 Power Supply, Ground, and Noise Considerations . . . . . . . . . . . . . . . . . . . .9–65 (I) D.1.4 Transmission Line Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–66 (I) D.1.5 Decoupling Capacitors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–67 (I) D.2 BOARD SOLDERING CONSIDERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–68 (I) D.3 HANDLING PRECAUTIONS AND ELECTROSTATIC DISCHARGE . . . . . . . . . . . . . .9–68 (I) D.4 REDUCTION OF ELECTROMAGNETIC INTERFERENCE . . . . . . . . . . . . . . . . . . . . .9–72 (I) D.5 HARDWARE DESIGN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–73 (I) D.5.1 Power Distribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–74 (I) D.5.2 EMI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–76 (I) D.5.3 Power Interruptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–77 (I) D.5.4 Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–78 (I) D.5.5 Product Testing and Design Validation . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–78 (I) TABLE OF CONTENTS MOTOROLA LONWORKS TECHNOLOGY viii D.5.6 Board Layout Issues and Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–79 (I) D.6 CMOS LATCH-UP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–80 (I) D.7 RECOMMENDED BYPASS CAPACITOR PLACEMENT . . . . . . . . . . . . . . . . . . . . . . .9–82 (I) APPENDIX E Neuron IC MEMORY MAPS 9–87 (I) APPENDIX F SUPPORT TOOLS 9–95 (I) BR1139 LONWORKS(cid:226) Support Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–96 (I) M143120DWEVK Neuron Chip Custom Node Development Board with 32-Pin Socket. . . .9–100 (I) M143120FBEVK Neuron Chip Custom Node Development Board with 44-Pin Socket . . . .9–103 (I) M143150EVK Neuron Chip Custom Node Development Board. . . . . . . . . . . . . . . . . . . . . .9–106 (I) M143204EVK LonBuilder Direct-Connect Transceiver Board. . . . . . . . . . . . . . . . . . . . . . . .9–110 (I) M143206EVK Neuron Chip Gizmo 3 I/O Interface Board. . . . . . . . . . . . . . . . . . . . . . . . . . .9–114 (I) M143208EVK I/O Interface Test Board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–117 (I) M143232EVK Voice Compression Board for LONWORKS Networks . . . . . . . . . . . . . . . . . . .9–121 (I) M143235EVK Neuron Chip Custom Node Development Board . . . . . . . . . . . . . . . . . . . . . .9–124 (I) MC143238EVK Neuron(cid:226) Chip LiteNode Development Boards . . . . . . . . . . . . . . . . . . . . . . 9-126 (I) APPENDIX G CUSTOMER ALERTS 9–132 (I) G.1 Neuron EEPROM PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–132 (I) G.2 Neuron CHIP HANDLING PRECAUTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–133 (I) G.3 USING ECHELON’S EMULATOR BOARDS WITH MOTOROLA’S DIRECT-CONNECT BOARD (M143204EVK). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–133 (I) G.4 LonBuilder 3.0 SOFTWARE REVISION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9–134 (I) APPENDIX H Neurowire (SPI INTERFACE) COMPATIBLE DEVICES 9–136 (I) APPENDIX I USAGE GUIDELINES FOR ECHELON TRADEMARKS 9–139 (I) SECTION EB ENGINEERING BULLETINS FROM ECHELON EB–1 (II) EB146 Neuron Chip Quadrature Input Function Interface. . . . . . . . . . . . . . . . . . . . . . . . . .EB–3 (II) EB147 LONWORKS Installation Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .EB–10 (II) EB148 Enhanced Media Access Control with Echelon’s LonTalk Protocol . . . . . . . . . . . .EB–27 (II) EB149 Optimizing LonTalk Response Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .EB–33 (II) EB151 Scanning a Keypad with the Neuron Chip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .EB–38 (II) EB153 Driving a Seven-Segment Display with the Neuron Chip. . . . . . . . . . . . . . . . . . . .EB–43 (II) EB155 Analog-to-Digital Conversion with the Neuron Chip. . . . . . . . . . . . . . . . . . . . . . . .EB–55 (II) EB157 Creating Neuron C Applications with the Gizmo 3. . . . . . . . . . . . . . . . . . . . . . . . .EB–82 (II) EB161 LonTalk Protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .EB–117 (II) EB167 A Hybrid System for Fast Synchronized Response . . . . . . . . . . . . . . . . . . . . . . .EB–144 (II) EB168 EIA-232C Serial Interfacing with the Neuron Chip. . . . . . . . . . . . . . . . . . . . . . . .EB–163 (II) MOTOROLA LONWORKS TECHNOLOGY TABLE OF CONTENTS ix EB169 LONWORKS 78 kbps Self-Healing Ring Architecture. . . . . . . . . . . . . . . . . . . . . . .EB–173 (II) EB172 LONWORKS Custom Node Development . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .EB–179 (II) EB173 The SNVT Master List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .EB–195 (II) EB174 Junction Box and Wiring Guidelines for Twisted Pair LONWORKS Networks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .EB–223 (II) EB176 File Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .EB–240 (II) EB177 LONWORKS Power Line SCADA Systems. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .EB–253 (II) EB178 Developing a Network Driver for the PC LonTalk Adapter . . . . . . . . . . . . . . . . . .EB–265 (II) EB179 Determinism in Industrial Computer Control Network Applications. . . . . . . . . . .EB–277 (II) SECTION AL APPLICATIONS LITERATURE AL–1 (III) AN781A Revised Data Interface Standards. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AL-3 AN1208 Parallel I/O Interface to the Neuron(cid:226) Chip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AL–9 (III) AN1211 Interfacing DACs and ADCs to the Neuron(cid:226) IC . . . . . . . . . . . . . . . . . . . . . . . . . AL–34 (III) AN1216 Setback Thermostat Design Using the Neuron(cid:226) IC . . . . . . . . . . . . . . . . . . . . . . AL–44 (III) AN1225 Fuzzy Logic and the Neuron(cid:226) Chip. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AL–55 (III) AN1247 MC683xx to Neuron(cid:226) Chip Parallel I/O Interface . . . . . . . . . . . . . . . . . . . . . . . . AL–74 (III) AN1248 Programmable Peripheral . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AL–85 (III) AN1250 Low Cost PC Interface to LONWORKS(cid:226) -Based Nodes. . . . . . . . . . . . . . . . . . . . AL–101 (III) AN1251 Programming the MC143120 Neuron(cid:226) IC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . AL–112 (III) AN1252 MIP Guidelines and Design Issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AL–145 (III) AN1266 LONWORKS(cid:226) Distributed Node Crane Demonstration . . . . . . . . . . . . . . . . . . . . AL–160 (III) AN1276 Installation of Neuron(cid:226) Chip-Based Products. . . . . . . . . . . . . . . . . . . . . . . . . . AL–175 (III) AN1278 LONWORKS(cid:226) Software Review. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AL–191 (III) AN1715 Fiber Optic LONWORKS(cid:226) Network Control Products from Raytheon Electronics AL–197 (III) TABLE OF CONTENTS MOTOROLA LONWORKS TECHNOLOGY x

Description: