Practical Digital Design: An Introduction to VHDL PDF

Preview Practical Digital Design: An Introduction to VHDL

PRACTICAL DIGITAL DESIGN PRACTICAL DIGITAL DESIGN: AN INTRODUCTION TO VHDL Bruce Reidenbach Purdue University Press, West Lafayette, Indiana Copyright 2022 by Purdue University. All rights reserved. Printed in the United States of America. Cataloging-in-Publication Data is available at the Library of Congress. 978-1-61249-766-2 (hardback) 978-1-61249-767-9 (epdf) Cover image: The cover photo of the Intel® Core™ i7 Nehalem microprocessor wafer is used by permission courtesy of Intel Corporation. The Quartus screen captures in chapter 14 are also used by permission of Intel Corporation. The gate array photograph on page 4 and the standard cell and gate array photographs on page 250 are used by permission courtesy of Dr. Antoine Bercovici of Siliconinsider. The full custom photograph on page 250 is used by permission courtesy of the National High Magnetic Field Laboratory at Florida State University. The Modelsim simulation waveform screen captures are used by permission courtesy of Mentor Graphics, a division of Siemens AG. The logic synthesis schematic examples and Vivado screen captures in chapters 14 through 17 are used by permission courtesy of Xilinx Incorporated. This book was entirely composed using The Document Foundation’s LibreOffice Writer word processor and LibreOffice Draw software. The book was typeset using Liberation Serif, Liberation Sans, and Liberation Mono fonts. This book is dedicated to the memory of our dog Buddy, who sadly passed away during the final stages of publication. He was a big, red, goofy, playful, loyal, loving dog and was constantly by my side while I was writing this book. In many ways he was my muse and was definitely my best friend throughout the pandemic. While he couldn’t answer any of my questions, he was always willing to lend an ear and a quick tail wag. TABLE OF CONTENTS PREFACE.................................................................................................................................xiii ACKNOWLEDGMENTS............................................................................................................xv ABOUT THE AUTHOR...........................................................................................................xvii CHAPTER 1 INTRODUCTION....................................................................................................1 Target Audience.....................................................................................................................1 A Brief History of Digital Design.............................................................................................2 The Need for a Hardware Description Language..................................................................8 A Brief Tour of a VHDL Model................................................................................................9 CHAPTER 2 SIGNALS, TIME, AND THE SIMULATION CYCLE.............................................15 Signals.................................................................................................................................15 Events............................................................................................................................18 Drivers............................................................................................................................18 Delta Time............................................................................................................................19 The Simulation Cycle...........................................................................................................21 CHAPTER 3 THE VHDL DESIGN ENVIRONMENT.................................................................33 Modeling Styles....................................................................................................................33 Design Flow.........................................................................................................................34 Data Types...........................................................................................................................35 Type Definition...............................................................................................................36 Vector Data Types..........................................................................................................37 Operators and Precedence..................................................................................................39 Design Libraries...................................................................................................................42 Predefined Packages...........................................................................................................43 STANDARD Package.....................................................................................................43 STD_LOGIC_1164 Package..........................................................................................44 NUMERIC_STD Package..............................................................................................46 TEXTIO Package...........................................................................................................48 Type Conversion..................................................................................................................49 Type Qualification................................................................................................................50 Attributes..............................................................................................................................51 TABLE OF CONTENTS VHDL Language Versions....................................................................................................52 Coding Style.........................................................................................................................52 Vertical Alignment...........................................................................................................53 VHDL Identifier Naming Rules.......................................................................................53 Comments......................................................................................................................54 CHAPTER 4 DECLARATIONS.................................................................................................57 Syntax Notation....................................................................................................................57 Object Declaration Syntax...................................................................................................58 Custom Type Declarations...................................................................................................58 Integer Types.................................................................................................................59 Floating Point Types.......................................................................................................60 Enumerated Types.........................................................................................................61 Array Types....................................................................................................................62 Record Types.................................................................................................................63 Physical Types...............................................................................................................64 Access Types.................................................................................................................65 Alias Declarations................................................................................................................66 CHAPTER 5 LIBRARIES AND DESIGN UNITS.......................................................................69 Library Units.........................................................................................................................69 Entity Declaration...........................................................................................................69 Ports.........................................................................................................................71 Generics...................................................................................................................74 Architecture Declaration.................................................................................................75 Package Declaration......................................................................................................78 Package Body Declaration.............................................................................................79 Configuration Declaration...............................................................................................81 Design Units.........................................................................................................................81 Context Clause....................................................................................................................82 Summary..............................................................................................................................83 CHAPTER 6 CONCURRENT STATEMENTS...........................................................................85 Conditional Signal Assignment Statement...........................................................................85 Selected Signal Assignment Statement...............................................................................88 Waveform Specification.......................................................................................................90 Delay Models.................................................................................................................91 Generate Statement.............................................................................................................92 Concurrent Assertion Statement..........................................................................................94 Component Instantiation......................................................................................................95 Component Declaration.................................................................................................96 Configuration Specification............................................................................................97 TABLE OF CONTENTS Component Instantiation Statement...............................................................................98 Direct Entity Instantiation.............................................................................................100 Block Statement.................................................................................................................101 Process Statement.............................................................................................................102 Summary............................................................................................................................104 CHAPTER 7 SEQUENTIAL STATEMENTS...........................................................................107 Null Statement...................................................................................................................107 Wait Statement..................................................................................................................108 If Statement........................................................................................................................109 Case Statement.................................................................................................................110 Loop Statement..................................................................................................................111 Loop Control Statements..............................................................................................112 Assertion and Report Statements......................................................................................113 Signal Assignment..............................................................................................................114 Variable Assignment...........................................................................................................116 Summary............................................................................................................................117 CHAPTER 8 THE PROCESS STATEMENT...........................................................................119 Process Review.................................................................................................................121 Combinatorial Logic...........................................................................................................122 Level Sensitive Latches.....................................................................................................123 Clocked Logic....................................................................................................................124 Process Examples.............................................................................................................131 Register Files...............................................................................................................131 Shift Registers..............................................................................................................132 Adders..........................................................................................................................135 Counters.......................................................................................................................138 State Machines............................................................................................................139 Memory Arrays.............................................................................................................140 Process Construction Guidelines.......................................................................................141 Summary............................................................................................................................142 CHAPTER 9 MODELING CASE STUDIES............................................................................145 Modeling Style...................................................................................................................145 Binary Adder......................................................................................................................147 Behavioral Model.........................................................................................................148 Synthesizable Model....................................................................................................149 Structural Model...........................................................................................................151 Summary......................................................................................................................152 Engine Management System.............................................................................................152

The list of books you might like

Can’t Hurt Me: Master Your Mind and Defy the Odds

The Mountain Is You

A Thousand Boy Kisses

Corrupt (Devil's Night #1)

By: Abu Ja'far Muhammad ibn Ali ibn Hussein ibn Musa ibn

Выступления полномочного представителя Президента РФ в Конституционном Суде Российской Федерации. 2015–2018 годы. Сборник. Том 2. 2017–2018 годы

DTIC ADA522305: Smooth Particle Hydrodynamics for Surf Zone Waves

Georgi E. Shilov – Linear Algebra

Old Testament Essentials: Creation, Conquest, Exile and Return (The Essentials Set)

Bürgerliches Recht II. Schuldrecht Allgemeiner Teil, 3. Auflage

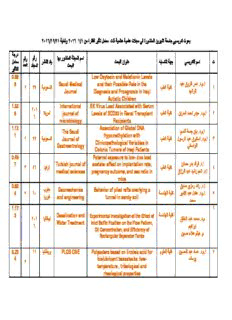

2016 / 12 / 21 ولغاية 2016 1 1

Einstein Product Metrics in Diverse Dimensions

![Verrassing: verliefd! (Wrangler's Creek 02)[Feelgood 18] book image](https://cdn-3.pdfdrive.to/media/content/thumbnails/17318296.jpg)

Verrassing: verliefd! (Wrangler's Creek 02)[Feelgood 18]

Greek Government Gazette: Part 7, 2006 no. 837

Desert Notes / River Notes

C-130 Airlift (USAF)

CARACTERIZACIÓN DE POLIFENOLES Y SU ACCIÓN SOBRE SIRTUÍNAS EN MODELOS DE

News from FormCalc and LoopTools

C ' ical management of abortion complications - World Health

Caracterização da Pesca Artesanal e Amadora na Área de Influência do Novo Porto

Luck on the Wing by Elmer Haslett

![SL(n,Z[t]) is not FP_{n-1} book image](https://cdn.pdfdrive.to/media/content/thumbnails/d5139d6f-df0f-47ff-a92e-7a36e43ce044.webp)