Table Of ContentG

March 2003 e

Revision 1.1 o

d

e

™

S

C

Geode™ SC1100 1

1

0

Information Appliance On a Chip 0

I

n

f

o

r

General Description m

a

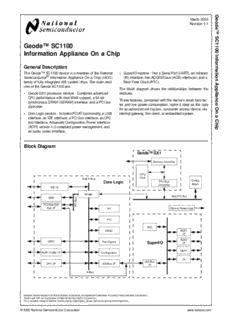

The Geode™ SC1100 device is a member of the National (cid:127) SuperI/O module - Has a Serial Port (UART), an Infrared t

Semiconductor® Information Appliance On a Chip (IAOC) (IR) interface, two ACCESS.bus (ACB) interfaces, and a io

n

family of fully integrated x86 system chips. The main mod- Real-Time Clock (RTC).

A

ules of the Geode SC1100 are:

The block diagram shows the relationships between the p

p

(cid:127) Geode GX1 processor module - Combines advanced modules. l

i

a

CPU performance with Intel MMX support, a 64-bit

These features, combined with the device’s small form fac- n

synchronous DRAM (SDRAM) interface, and a PCI bus c

tor and low power consumption, make it ideal as the core e

controller.

for an advanced set-top box, consumer access device, res- O

(cid:127) Core Logic module - Includes PC/AT functionality, a USB idential gateway, thin client, or embedded system. n

interface, an IDE interface, a PCI bus interface, an LPC a

C

bus interface, Advanced Configuration Power Interface

h

(ACPI) version 1.0 compliant power management, and i

p

an audio codec interface.

Block Diagram

Geode™ GX1

Memory Controller

CPU

Core

Fast X-Bus

Core Logic PCI Bus Config.

Controller Block

IDE I/F

Bridge

Fast-PCI Bus

USB s

u

B

PCI/Sub-ISA CI

P

Bus I/F PIT Clock & Reset Logic

PIC

RTC

DMAC ACB1

I/F

ACB2

GPIO Pwr Mgmnt SuperI/O I/F

UART

Audio Codec I/F Configuration

IR

ISA Bus

LPC I/F ISA Bus I/F

I/F

X-Bus

National Semiconductor and Virtual System Architecture are registered trademarks of National Semiconductor Corporation.

Geode and VSA are trademarks of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

© 2003 National Semiconductor Corporation www.national.com

0

0 Features

1

1

C

S General Features ■ Power Management:

™ — ACPI 1.0 compliant

■ 32-bit x86 processor, up to 300 MHz, with MMX instruc-

e — Sx state control of three power planes

d tion set support — Cx/Sx state control of clocks and PLLs

o

e ■ Memory controller with 64-bit SDRAM interface — Thermal event input

G

— Wakeup event support:

■ PC/AT functionality

– Three general-purpose events

■ PCI bus controller – UART RI# signal

– Infrared (IR) event

■ IDE interface, two channels

■ General Purpose I/Os (GPIOs):

■ USB, three ports, OHCI (OpenHost Controller Interface) — Six (6) dedicated GPIO signals

version 1.0 compliant — 24 multiplexed GPIO signals

■ Audio, AC97/AMC97 version 2.0 compliant ■ Low Pin Count (LPC) Bus Interface:

■ National’s Virtual System Architecture® technology — Specification version 1.0 compatible

(VSA™) support ■ PCI Bus Interface:

— PCI version 2.1 compliant with wakeup capability

■ Power management, ACPI (Advanced Configuration

— 32-bit data path, up to 33 MHz

Power Interface) version 1.0 compliant

— Glueless interface for an external PCI device

■ Package: — Supports four PCI bus master devices

— 388-Terminal TEPBGA (Thermally Enhanced Plastic — Supports four PCI interrupts

Ball Grid Array) — Rotating priority

— 3.3V signal support only

GX1 Processor Module

■ Sub-ISA Bus Interface:

■ CPU Core: — Supports up to four chip selects for external memory

— 32-bit x86 processor, up to 300 MHz, with MMX devices

instruction set support – Up to 16 MB addressing

— 16 KB unified L1 cache – Supports a chip select for ROM or Flash EPROM

— Integrated Floating Point Unit (FPU) boot device, up to 16 MB

— Re-entrant SMM (System Management Mode) – A chip select for one of:

enhanced for VSA – M-Systems’ DiskOnChip DOC2000 Flash file

system

■ Memory Controller:

– NAND EEPROM

— 64-bit SDRAM interface

— 78 to 100 MHz frequency range — Supports up to two chip selects for external I/O

— Direct interface with CPU/cache devices

— Supports clock suspend and power-down/self- – 8-bit (optional 16-bit) data bus width

refresh – Cycle multiplexed with PCI signals

— Up to 8 SDRAM devices or one DIMM/SODIMM – Is not the subtractive decode agent

■ IDE Interface:

Core Logic Module

— Two IDE channels for up to four external IDE devices

■ Audio Codec Interface: — Supports ATA-33 synchronous DMA mode transfers,

— AC97/AMC97 (Rev. 2.0) codec interface up to 33 MB/s

— Legacy audio emulation using XpressAUDIO

■ Universal Serial Bus (USB):

— Six DMA channels

— USB OpenHCI 1.0 compliant

■ PC/AT Functionality: — Three ports

— Programmable Interrupt Controller (PIC), 8259A-

equivalent

— Programmable Interval Timer (PIT), 8254-equivalent

— DMA Controller (DMAC), 8237-equivalent

www.national.com 2 Revision 1.1

G

SuperI/O Module Other Features e

o

■ Real-Time Clock (RTC): ■ High Resolution Timer: d

e

— DS1287, MC146818 and PC87911 compatible — 32-bit counter with 1 µs count interval ™

— Multi-century calendar ■ Watchdog: S

■ ACCESS.bus (ACB) Interface: — Interfaces to INTR, SMI, Reset C

1

— Two ACB interface ports 1

■ Clocks: 0

■ Serial Port (UART): — Input (external crystals): 0

— Enhanced UART – 32.768 KHz (internal clock oscillator)

– 27 MHz (internal clock oscillator)

■ Infrared (IR) Port

— Output:

— IrDA1.1 and 1.0 compatible

– AC97 clock (24.576MHz)

— Sharp-IR options ASK-IR and DASK-IR

– Memory controller clock (78 to 100MHz)

— Consumer Remote Control supports RC-5, RC-6,

– PCI clock (33MHz)

NEC, RCA and RECS80

— DMA support ■ JTAG Testability:

— Bypass, Extest, Sample/Preload, IDcode, Clamp, HiZ

■ Voltages

— Internal logic: 1.8V (233 MHz); 2.0V (266 MHz) or

TBD (300 MHz) ± 5%

— Battery: 3V ± 20%

— I/O: 3.3V ± 5%

— Standby: 3.3V ± 5% and 1.8V (233 MHz); 2.0V (266

MHz) or 2.0V (300 MHz) ± 5%

Revision 1.1 3 www.national.com

0

0 Table of Contents

1

1

C

S 1.0 Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

™

1.1 GX1 MODULE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

e

d 1.1.1 Integer Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

o

e 1.1.2 Floating Point Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

G

1.1.3 Write-Back Cache Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.1.4 Memory Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.1.5 Internal Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.1.6 Integrated Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

1.1.6.1 Memory Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

1.1.6.2 PCI Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

1.1.6.3 Fast-PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

1.1.7 Differences from Standalone GX1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

1.1.7.1 Device ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

1.1.7.2 SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

1.1.7.3 Slave PCI Burst Length Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.1.7.4 Scratchpad Size Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.1.7.5 Disable Virtual VGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.1.7.6 Disable Display Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.2 CORE LOGIC MODULE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

1.2.1 Other Interfaces of the Core Logic Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

1.3 SUPERI/O MODULE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

1.4 CLOCK, TIMERS, AND RESET LOGIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

1.4.1 Reset Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

1.4.1.1 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

1.4.1.2 System Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

2.0 Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.1 BALL ASSIGNMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

2.2 STRAP OPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

2.3 MULTIPLEXING CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

2.4 SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

2.4.1 System Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

2.4.2 Memory Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

2.4.3 ACCESS.bus Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

2.4.4 PCI Bus Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

2.4.5 Sub-ISA Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

2.4.6 Low Pin Count (LPC) Bus Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

2.4.7 IDE Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

2.4.8 Universal Serial Bus (USB) Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

2.4.9 Serial Port (UART) and Infrared (IR) Interface Signals . . . . . . . . . . . . . . . . . . . . . . .43

2.4.10 AC97 Audio Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

2.4.11 Power Management Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

2.4.12 GPIO Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

2.4.13 Debug Monitoring Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

2.4.14 JTAG Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

2.4.15 Test and Measurement Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

2.4.16 Power, Ground and No Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

www.national.com 4 Revision 1.1

G

Table of Contents (Continued) e

o

d

e

3.0 General Configuration Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 ™

3.1 CONFIGURATION BLOCK ADDRESSES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49 S

C

3.2 MULTIPLEXING, INTERRUPT SELECTION, AND BASE ADDRESS REGISTERS . . . . . . . .50

1

1

3.3 WATCHDOG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55 0

0

3.3.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

3.3.1.1 WATCHDOG Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

3.3.2 WATCHDOG Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

3.3.2.1 Usage Hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

3.4 HIGH-RESOLUTION TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

3.4.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

3.4.2 High-Resolution Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

3.4.2.1 Usage Hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

3.5 CLOCK GENERATORS AND PLLS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

3.5.1 27 MHz Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

3.5.2 GX1 Module Core Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

3.5.3 Internal Fast-PCI Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

3.5.4 SuperI/O Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

3.5.5 Core Logic Module Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

3.5.6 Clock Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

4.0 SuperI/O Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.1 FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

4.2 MODULE ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

4.3 CONFIGURATION STRUCTURE / ACCESS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.3.1 Index-Data Register Pair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.3.2 Banked Logical Device Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.3.3 Default Configuration Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

4.3.4 Address Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

4.4 STANDARD CONFIGURATION REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

4.4.1 SIO Control and Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

4.4.2 Logical Device Control and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

4.4.2.1 LDN 00h - Real-Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

4.4.2.2 LDN 01h - System Wakeup Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

4.4.2.3 LDN 02h - Infrared Communication Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

4.4.2.4 LDN 05h and 06h - ACCESS.bus Ports 1 and 2 . . . . . . . . . . . . . . . . . . . . . . . . . .78

4.4.2.5 LDN 08h - SP Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

4.5 REAL-TIME CLOCK (RTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

4.5.1 Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

4.5.2 RTC Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

4.5.2.1 Internal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

4.5.2.2 External Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

4.5.3 Timing Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

4.5.3.1 Timekeeping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

4.5.3.2 Alarms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

4.5.3.3 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

4.5.3.4 System Power States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

4.5.3.5 Oscillator Activity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

4.5.3.6 Interrupt Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

4.5.3.7 Battery-Backed RAMs and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

4.5.4 RTC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

4.5.4.1 Usage Hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

4.5.5 RTC General-Purpose RAM Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

Revision 1.1 5 www.national.com

0

0 Table of Contents

1 (Continued)

1

C

S 4.6 SYSTEM WAKEUP CONTROL (SWC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

™ 4.6.1 Event Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

e

4.6.2 SWC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

d

o

4.7 ACCESS.BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

e

G

4.7.1 Data Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

4.7.2 Start and Stop Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

4.7.3 Acknowledge (ACK) Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

4.7.4 Acknowledge After Every Byte Rule . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

4.7.5 Addressing Transfer Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

4.7.6 Arbitration on the Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

4.7.7 Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

4.7.7.1 Master Stop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

4.7.8 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

4.7.9 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

4.7.10 ACB Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

4.8 LEGACY FUNCTIONAL BLOCKS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

4.8.1 UART Functionality (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

4.8.1.1 UART Mode Register Bank Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

4.8.1.2 SP Register and Bit Maps for UART Functionality . . . . . . . . . . . . . . . . . . . . . . .105

4.8.2 IR Communications Port (IRCP) Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

4.8.2.1 IRCP Mode Register Bank Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

4.8.2.2 IRCP Register and Bit Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

5.0 Core Logic Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

5.1 FEATURE LIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

5.2 MODULE ARCHITECTURE AND CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

5.2.1 Fast-PCI Interface to External PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

5.2.1.1 Processor Mastered Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

5.2.1.2 External PCI Mastered Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

5.2.1.3 Core Logic Internal or Sub-ISA Mastered Cycles . . . . . . . . . . . . . . . . . . . . . . . .118

5.2.1.4 External PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

5.2.2 PSERIAL Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

5.2.3 IDE Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

5.2.3.1 IDE Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

5.2.3.2 PIO Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

5.2.3.3 Bus Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

5.2.3.4 UltraDMA/33 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

5.2.4 Universal Serial Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

5.2.5 Sub-ISA Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

5.2.5.1 Sub-ISA Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

5.2.5.2 Sub-ISA Support of Delayed PCI Transactions . . . . . . . . . . . . . . . . . . . . . . . . . .123

5.2.5.3 Sub-ISA Bus Data Steering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

5.2.5.4 I/O Recovery Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

5.2.5.5 ISA DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

5.2.5.6 ROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

5.2.5.7 PCI and Sub-ISA Signal Cycle Multiplexing . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

5.2.6 AT Compatibility Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

5.2.6.1 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

5.2.6.2 Programmable Interval Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

5.2.6.3 Programmable Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

5.2.7 I/O Ports 092h and 061h System Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

5.2.7.1 I/O Port 092h System Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

5.2.7.2 I/O Port 061h System Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

5.2.7.3 SMI Generation for NMI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

www.national.com 6 Revision 1.1

G

Table of Contents (Continued) e

o

d

e

5.2.8 Keyboard Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133 ™

5.2.8.1 Fast Keyboard Gate Address 20 and CPU Reset . . . . . . . . . . . . . . . . . . . . . . . .133

S

5.2.9 Power Management Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134 C

1

5.2.9.1 CPU States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

1

5.2.9.2 Sleep States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134 0

0

5.2.9.3 Power Planes Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

5.2.9.4 Power Management Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

5.2.9.5 Usage Hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

5.2.10 Power Management Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

5.2.10.1 APM Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

5.2.10.2 CPU Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

5.2.10.3 Peripheral Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

5.2.10.4 Power Management Programming Summary . . . . . . . . . . . . . . . . . . . . . . . . . . .142

5.2.11 GPIO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

5.2.12 Integrated Audio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

5.2.12.1 Data Transport Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

5.2.12.2 AC97 Codec Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146

5.2.12.3 VSA Technology Support Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

5.2.12.4 IRQ Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

5.2.13 LPC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

5.2.13.1 LPC Interface Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

5.2.13.2 Cycle Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

5.2.13.3 LPC Interface Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

5.3 REGISTER DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

5.3.1 PCI Configuration Space and Access Methods . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

5.3.2 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

5.4 CHIPSET REGISTER SPACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

5.4.1 Bridge, GPIO, and LPC Registers - Function 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

5.4.1.1 GPIO Support Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196

5.4.1.2 LPC Support Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

5.4.2 SMI Status and ACPI Registers - Function 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207

5.4.2.1 SMI Status Support Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208

5.4.2.2 ACPI Support Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .216

5.4.3 IDE Controller Registers - Function 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

5.4.3.1 IDE Controller Support Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .229

5.4.4 XpressAUDIO Registers - Function 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .231

5.4.4.1 XpressAUDIO Support Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .232

5.4.5 X-Bus Expansion Interface - Function 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246

5.4.5.1 X-Bus Expansion Support Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .250

5.4.6 USB Controller Registers - PCIUSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .251

5.4.7 ISA Legacy Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .265

6.0 Debugging and Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

6.1 TESTABILITY (JTAG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .279

6.1.1 Mandatory Instruction Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .279

6.1.2 Optional Instruction Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .279

6.1.3 JTAG Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .279

Revision 1.1 7 www.national.com

0

0 Table of Contents

1 (Continued)

1

C

S 7.0 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

™

7.1 GENERAL SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .280

e

d 7.1.1 Power/Ground Connections and Decoupling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .280

o

e 7.1.2 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .280

G

7.1.3 Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .281

7.1.4 DC Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .282

7.1.4.1 Power State Parameter Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .282

7.1.4.2 Definition and Measurement Techniques of SC1100 Current Parameters . . . . .282

7.1.4.3 Current Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283

7.1.5 Ball Capacitance and Inductance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .284

7.1.6 Pull-Up and Pull-Down Resistors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .285

7.2 DC CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .286

7.2.1 INAB DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .287

7.2.2 INBTN DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .287

7.2.3 INPCI DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .287

7.2.4 INT DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .287

7.2.5 INTS DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .288

7.2.6 INTS1 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .288

7.2.7 INUSB DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .289

7.2.8 ODn DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .289

7.2.9 ODPCI DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .289

7.2.10 Op/n DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .289

7.2.11 OPCI DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .290

7.2.12 OUSB DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .290

7.2.13 TSp/n DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .290

7.2.13.1 Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .290

7.3 AC CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .291

7.3.1 Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .292

7.3.2 ACCESS.bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .295

7.3.3 PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .298

7.3.3.1 Measurement and Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .301

7.3.4 Sub-ISA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .304

7.3.5 LPC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .308

7.3.6 IDE Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .309

7.3.7 Universal Serial Bus (USB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .327

7.3.8 Serial Port (UART) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .331

7.3.9 Fast IR Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332

7.3.10 Audio Interface Timing (AC97) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .333

7.3.11 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .338

7.3.12 Power-Up Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .339

7.3.13 JTAG Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .341

8.0 Package Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343

8.1 THERMAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .343

8.1.1 Heatsink Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .344

8.2 PHYSICAL DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .346

Appendix A Support Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347

A.1 ORDER INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .347

A.2 DATASHEET REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .347

www.national.com 8 Revision 1.1

G

1.0 Architecture Overview e

o

As illustrated in Figure 1-1, the SC1100 contains the follow- (cid:127) Core Logic Module: d

e

ing modules in one integrated device: — Includes PC/AT functionality, an IDE interface, a ™

Universal Serial Bus (USB) interface, ACPI 1.0

(cid:127) GX1 Module: S

compliant power management, and an audio codec

— Combines advanced CPU performance with MMX C

interface. 1

support, a 64-bit synchronous DRAM (SDRAM) inter- 1

face and a PCI bus controller. Integrates GX1 silicon (cid:127) SuperI/O Module: 0

0

revision 8.1.1. — Includes a Serial Port (UART), an Infrared (IR) inter-

face, two ACCESS.bus (ACB) interfaces, and a Real-

Time Clock (RTC).

Geode™ GX1

Memory Controller

CPU

Core

Fast X-Bus

Core Logic PCI Bus Config.

Controller Block

IDE I/F

Bridge

Fast-PCI Bus

USB s

u

B

PCI/Sub-ISA CI

P

Bus I/F PIT Clock & Reset Logic

PIC

RTC

DMAC ACB1

I/F

ACB2

GPIO Pwr Mgmnt SuperI/O I/F

UART

Audio Codec I/F Configuration

IR

ISA Bus

LPC I/F ISA Bus I/F

I/F

X-Bus

Figure 1-1. SC1100 Block Diagram

Revision 1.1 9 www.national.com

0

0 Architecture Overview

1 (Continued)

1

C

S 1.1 GX1 MODULE

™ The GX1 module (based upon silicon revision 8.1.1) is the The GX1 module is divided into major functional blocks (as

e central module of the SC1100. For detailed information shown in Figure 1-2):

d

o regarding the GX1 module, refer to the Geode GX1 Pro-

(cid:127) Integer Unit

e cessor Series datasheet and the Geode GX1 Processor

G

Series Silicon Revision 8.1.1 errata. The Geode GX1 mod- (cid:127) Floating Point Unit (FPU)

ule represents the sixth generation of x86-compatible 32-

(cid:127) Write-Back Cache Unit

bit processors with sixth-generation features. The decou-

pled load/store unit allows reordering of load/store traffic to (cid:127) Memory Management Unit (MMU)

achieve higher performance. Other features include single-

cycle execution, single-cycle instruction decode, 16 KB (cid:127) Internal Bus Interface Unit

write-back cache, and clock rates up to 300 MHz. These

(cid:127) Integrated Functions

features are made possible by the use of advanced-pro-

cess technologies and pipelining. Instructions are executed in the integer unit and in the float-

ing point unit. The cache unit stores the most recently used

The GX1 module has low power consumption at all clock

data and instructions and provides fast access to this infor-

frequencies. Where additional power savings are required,

mation for the integer and floating point units.

designers can make use of Suspend Mode, Stop Clock

capability, and System Management Mode (SMM).

Write-Back Integer

MMU FPU

Cache Unit Unit

C-Bus

Internal Bus Interface Unit

X-Bus

Integrated

Memory PCI

Functions

Controller Controller

SDRAM Port Fast-PCI Bus

Figure 1-2. Internal Block Diagram

www.national.com 10 Revision 1.1

Description:• Geode GX1 processor module - Combines advanced CPU performance with Intel MMX support, a 64-bit synchronous DRAM (SDRAM) interface, and a PCI bus controller.