Dual, 12-Bit, 3+3 or 2+2 Channel, Simultaneous Sampling ADC PDF

Preview Dual, 12-Bit, 3+3 or 2+2 Channel, Simultaneous Sampling ADC

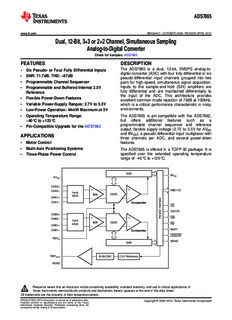

ADS7865 www.ti.com SBAS441C–OCTOBER2008–REVISEDAPRIL2012 Dual, 12-Bit, 3+3 or 2+2 Channel, Simultaneous Sampling Analog-to-Digital Converter CheckforSamples:ADS7865 FEATURES DESCRIPTION 1 • SixPseudo-orFour FullyDifferentialInputs The ADS7865 is a dual, 12-bit, 2MSPS analog-to- 2 digitalconverter(ADC)with four fullydifferentialorsix • SNR:71.7dB,THD:–87dB pseudo-differential input channels grouped into two • ProgrammableChannelSequencer pairs for high-speed, simultaneous signal acquisition. • Programmableand BufferedInternal2.5V Inputs to the sample-and-hold (S/H) amplifiers are Reference fully differential and are maintained differentially to the input of the ADC. This architecture provides • FlexiblePower-DownFeatures excellent common-mode rejection of 72dB at 100kHz, • VariablePower-SupplyRanges:2.7Vto5.5V which is a critical performance characteristic in noisy • Low-PowerOperation:44mW Maximumat5V environments. • OperatingTemperatureRange: The ADS7865 is pin-compatible with the ADS7862, –40°Cto+125°C but offers additional features such as a programmable channel sequencer and reference • Pin-CompatibleUpgradefor theADS7862 output, flexible supply voltage (2.7V to 5.5V for AV DD andBV ), apseudo-differentialinput multiplexerwith APPLICATIONS DD three channels per ADC, and several power-down • MotorControl features. • Multi-AxisPositioningSystems The ADS7865 is offered in a TQFP-32 package. It is • Three-PhasePowerControl specified over the extended operating temperature rangeof–40°Cto+125°C. SAR BV AV DD DD CHA0+ CHA0- DB[11:0] Input S/H CDAC MUX CHA1+ e CHA1- Comparator nterfac CS el I CLOCK CHB0+ all CHB0- Par WR Input S/H CDAC MUX RD CHB1+ CHB1- Comparator BUSY CONVST REF IN BGND SAR REFOUT 10-Bit DAC 2.5V Reference AGND 1 Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsof TexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet. Alltrademarksarethepropertyoftheirrespectiveowners. 2 PRODUCTIONDATAinformationiscurrentasofpublicationdate. Copyright©2008–2012,TexasInstrumentsIncorporated Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarilyincludetestingofallparameters. ADS7865 SBAS441C–OCTOBER2008–REVISEDAPRIL2012 www.ti.com This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriateprecautions.Failuretoobserveproperhandlingandinstallationprocedurescancausedamage. ESDdamagecanrangefromsubtleperformancedegradationtocompletedevicefailure.Precisionintegratedcircuitsmaybemore susceptibletodamagebecauseverysmallparametricchangescouldcausethedevicenottomeetitspublishedspecifications. ORDERING INFORMATION For the most current package and ordering information, see the Package Option Addendum at the end of this document,orvisitthedeviceproductfolderatwww.ti.com. ABSOLUTE MAXIMUM RATINGS(1) Overoperatingfree-airtemperaturerange,unlessotherwisenoted. ADS7865 UNIT Supplyvoltage,AVDDtoAGND –0.3to+6 V Supplyvoltage,BVDDtoBGND –0.3to+6 V Supplyvoltage,BVDDtoAVDD 1.5×AVDD V AnalogandreferenceinputvoltagewithrespecttoAGND AGND–0.3toAVDD+0.3 V DigitalinputvoltagewithrespecttoBGND BGND–0.3toBVDD+0.3 V Groundvoltagedifference|AGND–BGND| 0.3 V Inputcurrenttoallpinsexceptpower-supplypins –10to+10 mA Maximumvirtualjunctiontemperature,TJ +150 °C Humanbodymodel(HBM), ±4000 V JEDECstandard22,testmethodA114-C.01,allpins ESDratings Chargeddevicemodel(CDM), ±1500 V JEDECstandard22,testmethodC101,allpins (1) Stressesabovetheseratingsmaycausepermanentdamage.Exposuretoabsolutemaximumconditionsforextendedperiodsmay degradedevicereliability.Thesearestressratingsonly,andfunctionaloperationofthedeviceattheseoranyotherconditionsbeyond thosespecifiedisnotimplied. RECOMMENDED OPERATING CONDITIONS Overoperatingfree-airtemperaturerange,unlessotherwisenoted. ADS7865 PARAMETER MIN NOM MAX UNIT Supplyvoltage,AVDDtoAGND 2.7 5.0 5.5 V Lowvoltagelevels 2.7 3.6 V Supplyvoltage,BVDDtoBGND 5Vlogiclevels 4.5 5.0 5.5 V ReferenceinputvoltageonREFIN 0.5 2.5 2.525 V Analogdifferentialinputvoltage(CHXX+)–(CHXX–) –VREF +VREF V Operatingambienttemperaturerange,TA –40 +125 °C THERMAL CHARACTERISTICS(1) Overoperatingfree-airtemperaturerange,unlessotherwisenoted. PARAMETER ADS7865 UNIT θJA Junction-to-airthermalresistance High-Kthermalresistance 56.4 °C/W θJC Junction-to-casethermalresistance 20.8 °C/W PD DevicepowerdissipationatAVDD=5VandBVDD=3.3V 44 mW (1) TestedinaccordancewiththeHigh-KthermalmetricdefinitionsofEIA/JESD51-3forleadedsurface-mountpackageswitha3×3via array. 2 Copyright©2008–2012,TexasInstrumentsIncorporated ADS7865 www.ti.com SBAS441C–OCTOBER2008–REVISEDAPRIL2012 ELECTRICAL CHARACTERISTICS AtT =–40°Cto+125°C;overentirepower-supplyvoltagerange,V =2.5V(internal),f =32MHz,andf =2MSPS, A REF CLK DATA unlessotherwisenoted. ADS7865 PARAMETER TESTCONDITIONS MIN TYP(1) MAX UNIT RESOLUTION 12 Bits ANALOGINPUT FSR Full-scaledifferentialinputrange (CHxx+)–(CHxx–) –V +V V REF REF V Absoluteinputvoltage CHxx+orCHxx–toAGND –0.1 AV +0.1 V IN DD C Inputcapacitance CHxx+orCHxx–toAGND 2 pF IN C Differentialinputcapacitance 4 pF ID I Inputleakagecurrent –50 50 nA IL CMRR Common-moderejectionratio BothADCs,dcto100kHz 72 dB DCACCURACY –40°C<T <+125°C –1.25 ±0.6 +1.25 LSB A INL Integralnonlinearity –40°C<T <+85°C –1 ±0.5 +1 LSB A DNL Differentialnonlinearity –1 ±0.4 +1 LSB Inputoffseterror –3 ±0.5 +3 LSB V OS Match –3 ±0.5 +3 LSB dV /dT Inputoffsetthermaldrift ±2 μV/°C OS Gainerror –0.6 0.15 +0.6 % G ERR Match –0.6 ±0.1 +0.6 % G /dT Gainerrorthermaldrift ±2 ppm/°C ERR PSRR Power-supplyrejectionratio AV =5V 70 dB DD ACACCURACY SINAD Signal-to-noise+distortion V =5V at100kHz 69 71.3 dB IN PP SNR Signal-to-noiseratio V =5V at100kHz 70 71.7 dB IN PP THD Totalharmonicdistortion V =5V at100kHz –87 –74 dB IN PP SFDR Spurious-freedynamicrange V =5V at100kHz 74 88 dB IN PP SAMPLINGDYNAMICS t ConversiontimeperADC 1MHz<f ≤32MHz 13 Clocks CONV CLK t Acquisitiontime 62.5 ns ACQ f Datarate 1MHz<f ≤32MHz 62.5 2000 kSPS DATA CLK Aperturedelay 6 ns t A Match 50 ps t Aperturejitter 50 ps AJIT f ClockfrequencyonCLOCK 1 32 MHz CLK (1) AllvaluesatT =+25°C. A Copyright©2008–2012,TexasInstrumentsIncorporated 3 ADS7865 SBAS441C–OCTOBER2008–REVISEDAPRIL2012 www.ti.com ELECTRICAL CHARACTERISTICS (continued) AtT =–40°Cto+125°C;overentirepower-supplyvoltagerange,V =2.5V(internal),f =32MHz,andf =2MSPS, A REF CLK DATA unlessotherwisenoted. ADS7865 PARAMETER TESTCONDITIONS MIN TYP(1) MAX UNIT INTERNALVOLTAGEREFERENCE Resolution ReferenceoutputDACresolution 10 Bits Over20%to100%DACrange 0.496 2.515 V DAC=0x3FF, V Referenceoutputvoltage 2.485 2.500 2.515 V REFOUT –40°C<T <+125°C A DAC=0x3FFat+25°C 2.495 2.500 2.505 V dV /dT Referencevoltagedrift ±10 ppm/°C REFOUT DNL DACdifferentiallinearityerror –4 ±1 4 LSB DAC INL DACintegrallinearityerror –4 ±0.5 4 LSB DAC V DACoffseterror V =0.5V –4 ±1 4 LSB OSDAC REFOUT PSRR Power-supplyrejectionratio 73 dB I Referenceoutputdccurrent –2 +2 mA REFOUT Referenceoutputshort-circuit I 50 mA REFSC current t Referenceoutputsettlingtime 0.5 ms REFON VOLTAGEREFERENCEINPUT V Referenceinputvoltagerange 0.5 2.525 V REF I Referenceinputcurrent 50 μA REF C Referenceinputcapacitance 10 pF REF DIGITALINPUTS Logicfamily CMOS V High-levelinputvoltage 0.7×BV BV +0.3 V IH DD DD V Low-levelinputvoltage –0.3 0.3×BV V IL DD I Inputcurrent V =BV toBGND –50 +50 nA IN I DD C Inputcapacitance 5 pF I DIGITALOUTPUTS Logicfamily CMOS V High-leveloutputvoltage I =–100μA BV –0.2 V OH OH DD V Low-leveloutputvoltage I =100μA 0.2 V OL OH High-impedance-stateoutput I V =BV toBGND –50 +50 nA OZ current I DD C Outputcapacitance 5 pF O C Loadcapacitance 30 pF L 4 Copyright©2008–2012,TexasInstrumentsIncorporated ADS7865 www.ti.com SBAS441C–OCTOBER2008–REVISEDAPRIL2012 ELECTRICAL CHARACTERISTICS (continued) AtT =–40°Cto+125°C;overentirepower-supplyvoltagerange,V =2.5V(internal),f =32MHz,andf =2MSPS, A REF CLK DATA unlessotherwisenoted. ADS7865 PARAMETER TESTCONDITIONS MIN TYP(1) MAX UNIT POWERSUPPLY AV Analogsupplyvoltage AV toAGND 2.7 5.0 5.5 V DD DD BV BufferI/Osupplycurrent BV toBGND 2.7 3.0 5.5 V DD DD AV =2.7V 4.1 6.0 mA DD AV =5V 5.6 7.5 mA DD AV =2.7V,NAPpower-down 0.9 1.6 mA DD AI Analogsupplycurrent DD AV =5V,NAPpower-down 1.1 1.8 mA DD AV =2.7V,deeppower-down 0.001 mA DD AV =5V,deeppower-down 0.001 mA DD BV =2.7V,C =10pF 0.6 1.7 mA DD LOAD BI BufferI/Osupplycurrent DD BV =3.3V,C =10pF 0.8 1.9 mA DD LOAD AV =2.7V,BV =2.7V 12.7 21 mA DD DD P Powerdissipation D AV =5.0V,BV =3.0V 30.6 44 mW DD DD EQUIVALENT INPUT CIRCUIT R = 200W R = 50W SER SW CHXX+ C = 5pF C = 2pF PAR S C = 5pF C = 2pF PAR S CHXX- R = 200W R = 50W SER SW Copyright©2008–2012,TexasInstrumentsIncorporated 5 ADS7865 SBAS441C–OCTOBER2008–REVISEDAPRIL2012 www.ti.com DEVICE INFORMATION PBSPACKAGE TQFP-32 (TOPVIEW) + - + - - + - + 0 0 1 1 0 0 1 1 A A A A B B B B H H H H H H H H C C C C C C C C 32 31 30 29 28 27 26 25 REF 1 24 BV IN DD REFOUT 2 23 BGND AGND 3 22 WR AVDD 4 21 RD DB11 5 20 CS DB10 6 19 CLOCK DB9 7 18 CONVST DB8 8 17 BUSY 9 10 11 12 13 14 15 16 B7 B6 B5 B4 B3 B2 B1 B0 D D D D D D D D TERMINALFUNCTIONS PINNUMBER NAME DESCRIPTION 1 REF Referencevoltageinput.Aceramiccapacitorof470nF(min)isrequiredatthisterminal. IN 2 REF Referencevoltageoutput.Theprogrammableinternalvoltagereferenceoutputisavailableonthispin. OUT 3 AGND Analogground.Connecttoanaloggroundplane. 4 AV Analogpowersupply,2.7Vto5.5V.DecoupletoAGNDwitha1μFceramiccapacitor. DD 5 DB11 Databit11,MSB 6 DB10 Databit10 7 DB9 Databit9 8 DB8 Databit8 9 DB7 Databit7 10 DB6 Databit6 11 DB5 Databit5 12 DB4 Databit4 13 DB3 Databit3 14 DB2 Databit2 15 DB1 Databit1 16 DB0 Databit0 ADCbusyindicator.BUSYgoeshighwhentheinputsareinholdmodeandreturnstolowafterthe 17 BUSY conversionhasbeenfinished. Conversionstart.TheADCswitchesfromthesampleintotheholdmodeonthefallingedgeof 18 CONVST CONVST,independentofthestatusoftheCLOCK.Theconversionitselfstartswiththenextrising edgeofCLOCK. 19 CLOCK Externalclockinput. Chipselect.Whenlow,theparallelinterfaceofthedeviceisactive;whenhigh,inputsignalsare 20 CS ignoredandoutputsignalsare3-state. Readdata.Fallingedgeactivesynchronizationpulsefortheparalleldataoutputs.RDonlytriggers, 21 RD whenCSislow. 22 WR Writedata.Risingedgelatchesintheparalleldatainputs.WRonlytriggers,whenCSislow. 6 Copyright©2008–2012,TexasInstrumentsIncorporated ADS7865 www.ti.com SBAS441C–OCTOBER2008–REVISEDAPRIL2012 TERMINALFUNCTIONS(continued) PINNUMBER NAME DESCRIPTION 23 BGND BufferI/Oground.Connecttodigitalgroundplane. 24 BV BufferI/Opowersupply,2.7Vto5.5V.DecoupletoBGNDwitha1μFceramiccapacitor. DD 25 CHB1+ NoninvertinganaloginputchannelB1 26 CHB1– InvertinganaloginputchannelB1 27 CHB0+ NoninvertinganaloginputchannelB0 28 CHB0– InvertinganaloginputchannelB0 29 CHA1– InvertinganaloginputchannelA1 30 CHA1+ NoninvertinganaloginputchannelA1 31 CHA0– InvertinganaloginputchannelA0 32 CHA0+ NoninvertinganaloginputchannelA0 TIMING CHARACTERISTICS ConversionCycle tCONV 1 14 16 CLOCK tCLK t1 tCLKH tCLKL tACQ CONVST t2 t3 BUSY t4 t5 CS t6 t7 t8 t6 t7 WR t9 t14 RD t10 t12 t11 t13 DB[11:0] CHAx CHBx Input Output Output Data Previous ConversionResults Figure1. InterfaceTimingDiagram Copyright©2008–2012,TexasInstrumentsIncorporated 7 ADS7865 SBAS441C–OCTOBER2008–REVISEDAPRIL2012 www.ti.com TIMING REQUIREMENTS(1) ADS7865 PARAMETER TESTCONDITIONS MIN TYP MAX UNIT t Conversiontime f =32MHz 13 t CONV CLOCK CLK t Acquisitiontime 62.5 ns ACQ f CLOCKfrequency 1 32 MHz CLK t CLOCKperiod 31.25 1000 ns CLK t CLOCKlowtime 9.4 ns CLKL t CLOCKhightime 9.4 ns CLKH t CONVSTlowtime 20 ns 1 CONVSTfallingedgetoBUSYhigh t2 delay(2) 3 ns t CONVSThightime 20 ns 3 t RDfallingedgetoBUSYhighsetuptime 1 t 4 CLK t 14thCLOCKrisingedgetoBUSYlowdelay 3 ns 5 SeeFigure1 CSfallingedgetoRDorWRfallingedge t 0 ns 6 setuptime CSrisingedgetoRDorWRrisingedge t 0 ns 7 holdtime t WRlowtime 10 ns 8 t RDhightimebetweentworeadaccesses 10 ns 9 t RDfallingedgetooutputdatavaliddelay 20 ns 10 t Outputdataholdtime 5 ns 11 t Inputdatasetuptime 10 ns 12 t Inputdataholdtime 5 ns 13 InputdatastillvalidtoCONVSTfallingedge t 31.25 ns 14 setuptime (1) Allinputsignalsarespecifiedwitht =t =1.5ns(10%to90%ofBV )andtimedfromavoltagelevelof(V +V )/2. R F DD IL IH (2) Notapplicableinauto-Nappower-downmode. CLOCK Cycle1 Cycle2 10ns 10ns 5ns 5ns CONVST A B C NOTE:AllCONVSTcommandsthatoccurmorethan10nsbeforetherisingedgeofcycle'1'oftheexternalclock(Region'A')initiatea conversionontherisingedgeofcycle'1'.AllCONVSTcommandsthatoccur5nsaftertherisingedgeofcycle'1'or10nsbeforetherising edgeofcycle'2'(Region'B')initiateaconversionontherisingedgeofcycle'2'.AllCONVSTcommandsthatoccur5nsaftertherisingedge ofcycle'2'(Region'C')initiateaconversionontherisingedgeofthenextclockperiod. TheCONVSTpinshouldneverbeswitchedfromLOWtoHIGHintheregion10nsbeforetherisingedgeoftheCLOCKand5nsafterthe risingedge(grayareas).IfCONVSTistoggledinthisgrayarea,theconversioncouldbeginoneitherthesamerisingedgeoftheCLOCKor thefollowingedge. Figure2. CONVSTTiming 8 Copyright©2008–2012,TexasInstrumentsIncorporated ADS7865 www.ti.com SBAS441C–OCTOBER2008–REVISEDAPRIL2012 TYPICAL CHARACTERISTICS Overtheentiresupplyvoltagerange;V =2.5V(internal),f =32MHz,andf =2MSPS,unlessotherwisenoted. REF CLK DATA INTEGRALNONLINEARITYvs INTEGRALNONLINEARITYvs DATARATE TEMPERATURE 1.00 1.00 0.75 0.75 0.50 0.50 Positive Positive B) 0.25 B) 0.25 S S L (L 0 L (L 0 IN -0.25 IN -0.25 Negative Negative -0.50 -0.50 -0.75 -0.75 -1.00 -1.00 0.50 0.75 1.00 1.25 1.50 1.75 2.00 -40 -25 -10 5 20 35 50 65 80 95 110 125 Temperature (°C) Data Rate (MSPS) Figure3. Figure4. INTEGRALNONLINEARITYvsCODE DIFFERENTIALNONLINEARITYvsCODE 1.0 1.0 0.8 0.8 0.6 0.6 0.4 0.4 B) 0.2 B) 0.2 S S INL (L -0.20 DNL (L -0.20 -0.4 -0.4 -0.6 -0.6 -0.8 -0.8 -1.0 -1.0 0 512 1024 1536 2048 2560 3072 3584 4096 0 512 1024 1536 2048 2560 3072 3584 4096 Code Code Figure5. Figure6. DIFFERENTIALNONLINEARITYvs DIFFERENTIALNONLINEARITYvs DATARATE TEMPERATURE 1.00 1.00 0.75 0.75 0.50 0.50 Positive B) 0.25 B) 0.25 S Positive S L (L 0 L (L 0 N N D -0.25 D -0.25 Negative Negative -0.50 -0.50 -0.75 -0.75 -1.00 -1.00 0.50 0.75 1.00 1.25 1.50 1.75 2.00 -40 -25 -10 5 20 35 50 65 80 95 110 125 Data Rate (MSPS) Temperature (°C) Figure7. Figure8. Copyright©2008–2012,TexasInstrumentsIncorporated 9 ADS7865 SBAS441C–OCTOBER2008–REVISEDAPRIL2012 www.ti.com TYPICAL CHARACTERISTICS (continued) Overtheentiresupplyvoltagerange;V =2.5V(internal),f =32MHz,andf =2MSPS,unlessotherwisenoted. REF CLK DATA OFFSETERRORANDOFFSETMATCHvs OFFSETERRORANDOFFSETMATCHvs ANALOGSUPPLYVOLTAGE TEMPERATURE 1.0 2.0 B) 0.8 B) S OffsetMatch S 1.5 L L ch ( 0.6 ch ( 1.0 Mat 0.4 Offset Error Mat Offset Match et 0.2 et 0.5 s s Offset Error Off 0 Off 0 and -0.2 and -0.5 or -0.4 or Err Err -1.0 et -0.6 et Offs -0.8 Offs -1.5 -1.0 -2.0 2.7 3.0 3.3 3.6 3.9 4.2 4.5 4.8 5.1 5.4 -40 -25 -10 5 20 35 50 65 80 95 110 125 AV (V) Temperature (°C) DD Figure9. Figure10. GAINERRORANDGAINMATCHvs GAINERRORANDGAINMATCHvs ANALOGSUPPLYVOLTAGE TEMPERATURE 0.5 0.20 Gain Error %) 0.4 %) 0.15 ch ( 0.3 ch ( 0.10 Mat 0.2 Gain Error Mat Gain Match n 0.1 n 0.05 ai ai d G 0 Gain Match d G 0 n n or a -0.1 or a -0.05 ain Err --00..23 ain Err -0.10 G -0.4 G -0.15 -0.5 -0.20 2.7 3.0 3.3 3.6 3.9 4.2 4.5 4.8 5.1 5.4 -40 -25 -10 5 20 35 50 65 80 95 110 125 AV (V) Temperature (°C) DD Figure11. Figure12. COMMON-MODEREJECTIONRATIOvs COMMON-MODEREJECTIONRATIOvs ANALOGSUPPLYVOLTAGE TEMPERATURE 74.0 74.0 73.5 73.5 73.0 73.0 B) 72.5 B) 72.5 d d R ( 72.0 R ( 72.0 R R M M C 71.5 C 71.5 71.0 71.0 70.5 70.5 70.0 70.0 2.7 3.0 3.3 3.6 3.9 4.2 4.5 4.8 5.1 5.4 -40 -25 -10 5 20 35 50 65 80 95 110 125 AV (V) Temperature (°C) DD Figure13. Figure14. 10 Copyright©2008–2012,TexasInstrumentsIncorporated

Description: