12-, 14-, and 16-Bit, 8-Channel, Simultaneous Sampling ADCs PDF

Preview 12-, 14-, and 16-Bit, 8-Channel, Simultaneous Sampling ADCs

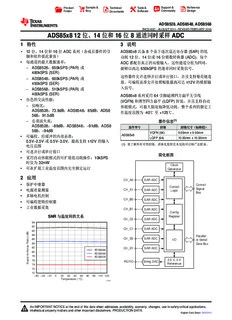

Product Sample & Technical Tools & Support & Reference Folder Buy Documents Software Community Design ADS8528,ADS8548,ADS8568 ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 ADS85x8 12 位位、、14 位位和和 16 位位 8 通通道道同同时时采采样样 ADC 1 特特性性 3 说说明明 • 12位、14位和16位ADC系列(各成员器件的引 ADS85x8具备8 个基于逐次逼近寄存器(SAR)的低 1 脚和软件彼此兼容) 功耗12位、14位或16位模数转换器(ADC),每个 • 每通道的最大数据速率: ADC都配有真正的双极输入。这些通道分组为四对, – ADS8528:650kSPS(PAR) 或 能够以高达650kSPS的速率同时采集信号。 480kSPS(SER) 这些器件允许选择并行或串行接口,并且支持菊花链连 – ADS8548:600kSPS(PAR) 或 接。可编程基准允许处理幅值最高可达±12V 的模拟输 450kSPS(SER) 入信号。 – ADS8568:510kSPS(PAR) 或 400kSPS(SER) ADS85x8系列采用64引脚超薄四方扁平无引线 • 出色的交流性能: (VQFN)和薄型四方扁平(LQFP) 封装,并且支持自动 – 信噪比: 休眠模式,可最大限度地降低功耗。整个系列的额定工 ADS8528:73.9dB;ADS8548:85dB;ADS8 作温度范围为-40℃至+125℃。 568:91.5dB – 总谐波失真: 器器件件信信息息(1) ADS8528:–89dB;ADS8548:–91dB;ADS8 器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值)) 568:–94dB VQFN(64) 9.00mmx9.00mm • 可编程、经缓冲的内部基准: ADS85x8 LQFP(64) 10.00mmx10.00mm 0.5V–2.5V 或0.5V–3.0V,最高支持±12V 的输入 (1) 要了解所有可用封装,请参见数据表末尾的可订购产品附录。 电压范围 • 可选并行或串行接口 简简化化框框图图 • 采用自动休眠模式的可扩展低功耗操作:10kSPS 时仅为32mW Clock • 可在扩展工业温度范围内完全额定运行 Generator 2 应应用用 CH_A0 SAR ADC • 保护中继器 Control Control • 电源质量测量 CH_A1 SAR ADC Logic Signal Bus • 多轴电机控制 CH_B0 SAR ADC • 可编程逻辑控制器 • 工业数据采集 CH_B1 SAR ADC Config SNR与与温温度度间间的的关关系系 Register CH_C0 SAR ADC 94 92 CH_C1 SAR ADC 90 B) atio (d 8868 CH_D0 SAR ADC I/O Pora Sraellreiall R 84 Data Bus e Nois 8802 ADS8568 CH_D1 SAR ADC o- ADS8548 al-t 78 ADS8528 gn 76 REFIO String DAC 2.5-V, 3-V Si 74 Reference 72 70 −40 −25 −10 5 20 35 50 65 80 95 110 125 Temperature (°C) G016 1 AnIMPORTANTNOTICEattheendofthisdatasheetaddressesavailability,warranty,changes,useinsafety-criticalapplications, intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA. EnglishDataSheet:SBAS543 ADS8528,ADS8548,ADS8568 ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 www.ti.com.cn 目目录录 1 特特性性.......................................................................... 1 8.1 EquivalentCircuits..................................................26 2 应应用用.......................................................................... 1 9 DetailedDescription............................................ 26 3 说说明明.......................................................................... 1 9.1 Overview.................................................................26 4 修修订订历历史史记记录录........................................................... 2 9.2 FunctionalBlockDiagram.......................................27 9.3 FeatureDescription.................................................28 5 DeviceComparisonTable..................................... 4 9.4 DeviceFunctionalModes........................................34 6 PinConfigurationandFunctions......................... 4 9.5 RegisterMaps ........................................................39 7 Specifications......................................................... 9 10 ApplicationandImplementation........................ 41 7.1 AbsoluteMaximumRatings......................................9 10.1 ApplicationInformation..........................................41 7.2 ESDRatings..............................................................9 10.2 TypicalApplication................................................41 7.3 RecommendedOperatingConditions.......................9 11 PowerSupplyRecommendations..................... 46 7.4 ThermalInformation..................................................9 12 Layout................................................................... 46 7.5 ElectricalCharacteristics:General..........................10 7.6 ElectricalCharacteristics:ADS8528.......................13 12.1 LayoutGuidelines.................................................46 7.7 ElectricalCharacteristics:ADS8548.......................14 12.2 LayoutExample....................................................47 7.8 ElectricalCharacteristics:ADS8568.......................15 13 器器件件和和文文档档支支持持..................................................... 48 7.9 SerialInterfaceTimingRequirements.....................16 13.1 文档支持...............................................................48 7.10 ParallelInterfaceTimingRequirements(Read 13.2 相关链接................................................................48 Access)....................................................................17 13.3 社区资源................................................................48 7.11 ParallelInterfaceTimingRequirements(Write 13.4 商标....................................................................... 48 Access)....................................................................17 13.5 静电放电警告.........................................................48 7.12 TypicalCharacteristics..........................................20 13.6 Glossary................................................................48 8 ParameterMeasurementinformation................26 14 机机械械、、封封装装和和可可订订购购信信息息....................................... 48 4 修修订订历历史史记记录录 注:之前版本的页码可能与当前版本有所不同。 ChangesfromRevisionB(November2015)toRevisionC Page • ChangedFigure45:changedcapacitorvaluesfrom820nFto820pF .............................................................................. 42 ChangesfromRevisionA(October2011)toRevisionB Page • 已添加ESD额定值表,建议运行条件表,特性描述部分,器件功能模式部分,寄存器映射部分,应用和实施部分, 电源相关建议部分,布局部分,器件和文档支持部分以及机械、封装和可订购信息部分....................................................... 1 • ChangedtitleofDeviceComparisonTable,deletedfootnote1 ............................................................................................ 4 • AddedStoragetemperatureparametertoAbsoluteMaximumRatingstable........................................................................ 9 • ChangedClockcyclesperconversiontobeasingleparameterinsteadofpartoft parameterinSerialInterface CONV TimingRequirementstable.................................................................................................................................................. 16 • Changedt parameterinSerialInterfaceTimingRequirementstable............................................................................ 16 BUFS • Addedfootnote3toSerialInterfaceTimingRequirementstable......................................................................................... 16 • ChangedClockcyclesperconversiontobeasingleparameterinsteadofpartoft parameterinParallel CONV InterfaceTimingRequirements(ReadAccess)table .......................................................................................................... 17 • Changedt parameterinParallelInterfaceTimingRequirements(ReadAccess)table ............................................... 17 BUCS • Addedfootnote3toParallelInterfaceTimingRequirements(ReadAccess)table ............................................................ 17 • ChangedDataReadoutandBUSY/INTSignalsection........................................................................................................ 30 • AddedSequentialOperationsection.................................................................................................................................... 31 • ChangeddescriptionofinitiatinganewconversioninResetandPower-DownModessection.......................................... 38 2 版权©2011–2016,TexasInstrumentsIncorporated ADS8528,ADS8548,ADS8568 www.ti.com.cn ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 ChangesfromOriginal(August2011)toRevisionA Page • DeletedINLcolumnfromFamily/OrderingInformationtable................................................................................................. 4 • ChangedDCAccuracy,INLparameterinADS8568ElecticalChatacteristicstable............................................................ 15 Copyright©2011–2016,TexasInstrumentsIncorporated 3 ADS8528,ADS8548,ADS8568 ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 www.ti.com.cn 5 Device Comparison Table RESOLUTION MAXIMUMDATARATE:PAR,SER SNR THD PRODUCT (Bits) (kSPSperChannel) (dB,Typ) (dB,Typ) ADS8528 12 650,480 73.9 –89 ADS8548 14 600,450 85 –91 ADS8568 16 510,400 91.5 –94 6 Pin Configuration and Functions RGCPackage 64-PinVQFN TopView _C0 FCP ND DD FCN _C1 ND DD FIO FN _B1 FBN DD ND FBP _B0 H E G V E H G V E E H E V G E H C R A A R C A A R R C R A A R C 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 6 6 6 6 6 5 5 5 5 5 5 5 5 5 5 4 HVSS 1 48 HVDD CH_D1 2 47 CH_A1 REFDN 3 46 REFAN AVDD 4 45 AVDD AGND 5 44 AGND REFDP 6 43 REFAP CH_D0 7 42 CH_A0 PAR/SER 8 7.3-mm x 7.3-mm 41 HW/SW STBY 9 Exposed Thermal Pad 40 CONVST_D RESET 10 39 CONVST_C REFEN/WR 11 38 CONVST_B RD 12 37 CONVST_A CS/FS 13 36 ASLEEP AVDD 14 35 BUSY/INT AGND 15 34 RANGE/XCLK DB15/SDO_D 16 33 DB0/DCIN_D 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 1 1 2 2 2 2 2 2 2 2 2 2 3 3 3 DB14/SDO_C DB13/SDO_B DB12/SDO_A 1/REFBUFEN DB10/SCLK DB9/SDI DB8/DCEN DGND DVDD DB7 DB6/SEL_B DB5/SEL_CD DB4 DB3/DCIN_A DB2/DCIN_B DB1/DCIN_C 1 B D 4 Copyright©2011–2016,TexasInstrumentsIncorporated ADS8528,ADS8548,ADS8568 www.ti.com.cn ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 PMPackage 64-PinLQFP TopView _C0 FCP ND DD FCN _C1 ND DD FIO FN _B1 FBN DD ND FBP _B0 H E G V E H G V E E H E V G E H C R A A R C A A R R C R A A R C 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 6 6 6 6 6 5 5 5 5 5 5 5 5 5 5 4 HVSS 1 48 HVDD CH_D1 2 47 CH_A1 REFDN 3 46 REFAN AVDD 4 45 AVDD AGND 5 44 AGND REFDP 6 43 REFAP CH_D0 7 42 CH_A0 PAR/SER 8 41 HW/SW STBY 9 40 CONVST_D RESET 10 39 CONVST_C REFEN/WR 11 38 CONVST_B RD 12 37 CONVST_A CS/FS 13 36 ASLEEP AVDD 14 35 BUSY/INT AGND 15 34 RANGE/XCLK DB15/SDO_D 16 33 DB0/DCIN_D 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 1 1 2 2 2 2 2 2 2 2 2 2 3 3 3 DB14/SDO_C DB13/SDO_B DB12/SDO_A 1/REFBUFEN DB10/SCLK DB9/SDI DB8/DCEN DGND DVDD DB7 DB6/SEL_B DB5/SEL_CD DB4 DB3/DCIN_A DB2/DCIN_B DB1/DCIN_C 1 B D Copyright©2011–2016,TexasInstrumentsIncorporated 5 ADS8528,ADS8548,ADS8568 ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 www.ti.com.cn PinFunctions PIN DESCRIPTION TYPE(1) NAME NO. PARALLELINTERFACE(PAR/SER=0) SERIALINTERFACE(PAR/SER=1) 5,15,44, AGND P Analogground;connecttotheanaloggroundplane. 51,58,62 Auto-sleepenableinput. Whenlow,thedeviceoperatesinnormalmode. Whenhigh,thedevicefunctionsinauto-sleepmodewheretheholdmodeandtheactualconversionisactivated ASLEEP 36 DI sixconversionclock(tCCLK)cyclesafterissuingaconversionstartusingaCONVST_x.Thismodeis recommendedtosavepowerifthedevicerunsatalowerdatarate;seetheResetandPower-DownModes sectionformoredetails. 4,14,45, Analogpowersupply. AVDD P 52,57,61 DecoupleaccordingtothePowerSupplyRecommendationssection. WhenCONFIGbitC27=0(BUSY/INT),thispinisaconverterbusystatusoutput. Thispintransitionshighwhenaconversionisstartedandtransitionslowforasingleconversionclockcycle (tCCLK)wheneverachannelpairconversioniscompletedandstayslowwhentheconversionofthelastchannel paircompletes. BUSY/INT 35 DO WhenbitC27=1(BUSY/INTinCONFIG),thispinisaninterruptoutput.Thispintransitionshighaftera conversioncompletesandremainshighuntilthenextreadaccess.Thismodecanonlybeusedifalleight channelsaresampledsimultaneously(allCONVST_xtiedtogether).ThepolarityoftheBUSY/INToutputcanbe changedusingtheC26bit(BUSYL/H)intheConfigurationregister. AnaloginputofchannelA0;channelAisthemasterchannelpairthatisalwaysactive. TheinputvoltagerangeiscontrolledbytheRANGEpininhardwaremodeorbyConfigurationregister(CONFIG) CH_A0 42 AI bitC24(RANGE_A)insoftwaremode.Incaseswherechannelpairsofthedeviceareusedatdifferentdata rates,channelpairAmustalwaysrunatthehighestdatarate. AnaloginputofchannelA1;channelAisthemasterchannelpairthatisalwaysactive. TheinputvoltagerangeiscontrolledbytheRANGEpininhardwaremodeorbyCONFIGbitC24(RANGE_A)in CH_A1 47 AI softwaremode.Incaseswherechannelpairsofthedeviceareusedatdifferentdatarates,channelpairAmust alwaysrunatthehighestdatarate. AnaloginputofchannelB0.TheinputvoltagerangeiscontrolledbytheRANGEpininhardwaremodeorby CH_B0 49 AI CONFIGbitC23(RANGE_B)insoftwaremode. AnaloginputofchannelB1.TheinputvoltagerangeiscontrolledbytheRANGEpininhardwaremodeorby CH_B1 54 AI CONFIGbitC23(RANGE_B)insoftwaremode. AnaloginputofchannelC0.TheinputvoltagerangeiscontrolledbytheRANGEpininhardwaremodeorby CH_C0 64 AI CONFIGbitC21(RANGE_C)insoftwaremode. AnaloginputofchannelC1.TheinputvoltagerangeiscontrolledbytheRANGEpininhardwaremodeorby CH_C1 59 AI CONFIGbitC21(RANGE_C)insoftwaremode. AnaloginputofchannelD0.TheinputvoltagerangeiscontrolledbytheRANGEpininhardwaremodeorby CH_D0 7 AI CONFIGbitC19(RANGE_D)insoftwaremode.ThispincanbepowereddownusingCONFIGbitC18(PD_D)in softwaremode. AnaloginputofchannelD1.TheinputvoltagerangeiscontrolledbytheRANGEpininhardwaremodeorby CH_D1 2 AI CONFIGbitC19(RANGE_D)insoftwaremode.ThispincanbepowereddownusingCONFIGbitC18(PD_D)in softwaremode. ConversionstartofchannelpairA. TherisingedgeofthissignalinitiatessimultaneousconversionofanalogsignalsatinputsCH_A[1:0]. CONVST_A 37 DI Thissignalresetstheinternalchannelstatemachinethatcausesthedataoutputtostartwithconversionresults ofchannelA0withthenextreadaccess. ConversionstartofchannelpairB. CONVST_B 38 DI TherisingedgeofthissignalinitiatessimultaneousconversionofanalogsignalsatinputsCH_B[1:0]. ConversionstartofchannelpairC. CONVST_C 39 DI TherisingedgeofthissignalinitiatessimultaneousconversionofanalogsignalsatinputsCH_C[1:0]. ConversionstartofchannelpairD. CONVST_D 40 DI TherisingedgeofthissignalinitiatessimultaneousconversionofanalogsignalsatinputsCH_D[1:0]. Chip-selectinput. Framesynchronization. CS/FS 13 DI,DI Whenlow,theparallelinterfaceisenabled. TheFSfallingedgecontrolstheframetransfer. Whenhigh,theinterfaceisdisabled. WhenDCEN=1andSEL_CD=1,thispinisthedaisy-chaindata DB0/DCIN_D 33 DIO,DI Databit0(LSB)input/output inputforSDO_Dofthepreviousdeviceinthechain. WhenDCEN=0,connecttoDGND. WhenDCEN=1andSEL_CD=1,thispinisthedaisy-chaindata DB1/DCIN_C 32 DIO,DI Databit1input/output inputforSDO_Cofthepreviousdeviceinthechain. WhenDCEN=0,connecttoDGND. WhenDCEN=1andSEL_B=1,thispinisthedaisy-chaindata DB2/DCIN_B 31 DIO,DI Databit2input/output inputforSDO_Bofthepreviousdeviceinthechain. WhenDCEN=0,connecttoDGND. WhenDCEN=1,thispinisthedaisy-chaindatainputforSDO_A DB3/DCIN_A 30 DIO,DI Databit3input/output ofthepreviousdeviceinthechain.WhenDCEN=0,connectto DGND. (1) AI=analoginput;AIO=analoginput/output;DI=digitalinput;DIO=digitalinput/output;DO=digitaloutput;andP=powersupply. 6 Copyright©2011–2016,TexasInstrumentsIncorporated ADS8528,ADS8548,ADS8568 www.ti.com.cn ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 PinFunctions (continued) PIN DESCRIPTION TYPE(1) NAME NO. PARALLELINTERFACE(PAR/SER=0) SERIALINTERFACE(PAR/SER=1) DB4 29 DIO Databit4input/output ConnecttoDGND SelectSDO_CandSDO_Dinput. Whenhigh,datafromchannelpairCareavailableonSDO_Cand datafromchannelpairDareavailableonSDO_D.Whenlowand DB5/SEL_CD 28 DIO,DI Databit5input/output SEL_B=1,datafromchannelpairsAandCareavailableon SDO_AanddatafromchannelpairsBandDareavailableon SDO_B.WhenlowandSEL_B=0,datafromalleightchannels areavailableonSDO_A. SelectSDO_Binput. Whenlow,SDO_Bisdisabledanddatafromalleightchannelsare onlyavailablethroughSDO_A. DB6/SEL_B 27 DIO,DI Databit6input/output WhenhighandSEL_CD=0,datafromchannelpairsBandDare availableonSDO_B.WhenSEL_CD=1,datafromchannelpairB areavailableonSDO_B. DB7 26 DIO Databit7input/output MustbeconnectedtoDGND Daisy-chainenableinput. DB8/DCEN 23 DIO,DI Databit8input/output Whenhigh,DB[3:0]serveasdaisy-chaininputsDCIN_[A:D]. Ifdaisy-chainmodeisnotused,connecttoDGND. Hardwaremode(HW/SW=0):connecttoDGND. DB9/SDI 22 DIO,DI Databit9input/output Softwaremode(HW/SW=1):serialdatainput. DB10/SCLK 21 DIO,DI Databit10input/output Serialinterfaceclockinput. Hardwaremode(HW/SW=0):referencebufferenableinput. Whenlow,allinternalreferencebuffersareenabled(mandatoryif internalreferenceisused). DB11/ 20 DIO,DI Databit11input/output. Whenhigh,allreferencebuffersaredisabled. REFBUFEN OutputisMSBfortheADS8528. Softwaremode(HW/SW=1):connecttoDGNDorDVDD. TheinternalreferencebuffersarecontrolledbyCONFIGbitC14 (REFBUFEN). DataoutputforchannelpairA. WhenSEL_CD=0,datafromchannelpairCarealsoavailableon Databit12input/output. DB12/SDO_A 19 DIO,DO thisoutput. OutputissignextensionfortheADS8528. WhenSEL_CD=0andSEL_B=0,SDO_Afunctionsassingle dataoutputforalleightchannels. Databit13input/output. WhenSEL_B=1,thispinisthedataoutputforchannelpairB. DB13/SDO_B 18 DIO,DO OutputissignextensionfortheADS8528 WhenSEL_B=0,tiethispintoDGND.WhenSEL_CD=0,data andMSBfortheADS8548. fromchannelpairDarealsoavailableonthisoutput. Databit14input/output. WhenSEL_CD=1,thispinisthedataoutputforchannelpairC. DB14/SDO_C 17 DIO,DO OutputissignextensionfortheADS8528 WhenSEL_CD=0,tiethispintoDGND. andADS8548. Databit15(MSB)input/output. WhenSEL_CD=1,thispinisthedataoutputforchannelpairD. DB15/SDO_D 16 DIO,DO OutputissignextensionfortheADS8528 WhenSEL_CD=0,tiethispintoDGND. andADS8548. DGND 24 P BufferI/Oground,connecttodigitalgroundplane BufferI/Osupply,connecttodigitalsupply. DVDD 25 P DecoupleaccordingtothePowerSupplyRecommendationssection. Positivesupplyvoltagefortheanaloginputs. HVDD 48 P DecoupleaccordingtothePowerSupplyRecommendationssection. Negativesupplyvoltagefortheanaloginputs. HVSS 1 P DecoupleaccordingtothePowerSupplyRecommendationssection. Modeselectioninput. Whenlow,hardwaremodeisselectedandthedevicefunctionsaccordingtothesettingsoftheexternalpins. HW/SW 41 DI Whenhigh,softwaremodeisselectedandthedeviceisconfiguredbywritingtotheConfigurationregister (CONFIG). Interfacemodeselectioninput. PAR/SER 8 DI Whenlow,theparallelinterfaceisselected.Whenhigh,theserialinterfaceisenabled. Hardwaremode(HW/SW=0):analoginputvoltagerangeselectinput. Whenlow,theanaloginputvoltagerangeis±4VREF.Whenhigh,theanaloginputvoltagerangeis±2VREF. RANGE/XCLK 34 DI/DI/DO Softwaremode(HW/SW=1):thispinisanexternalconversionclockinputifCONFIGbitC29=1(CLKSEL);or aninternalconversionclockoutputifCONFIGbitC28=1(CLKOUT_EN). Ifthispinisnotused,connecttoDGND. Readdatainput. Whenlow,theparalleldataoutputis RD 12 DI/DI MustbeconnectedtoDGND. enabled(ifCS=0).Whenhigh,thedata outputisdisabled. Copyright©2011–2016,TexasInstrumentsIncorporated 7 ADS8528,ADS8548,ADS8568 ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 www.ti.com.cn PinFunctions (continued) PIN DESCRIPTION TYPE(1) NAME NO. PARALLELINTERFACE(PAR/SER=0) SERIALINTERFACE(PAR/SER=1) DecouplingcapacitorinputforreferenceofchannelpairA. REFAN 46 AI ConnecttothedecouplingcapacitorandAGNDaccordingtothePowerSupplyRecommendationssection. DecouplingcapacitorinputforreferenceofchannelpairA. REFAP 43 AI ConnecttothedecouplingcapacitoraccordingtothePowerSupplyRecommendationssection. DecouplingcapacitorinputforreferenceofchannelpairB. REFBN 53 AI ConnecttothedecouplingcapacitorandAGNDaccordingtothePowerSupplyRecommendationssection. DecouplingcapacitorinputforreferenceofchannelpairB. REFBP 50 AI ConnecttothedecouplingcapacitoraccordingtothePowerSupplyRecommendationssection. DecouplingcapacitorinputforreferenceofchannelpairC. REFCN 60 AI ConnecttothedecouplingcapacitorandAGNDaccordingtothePowerSupplyRecommendationssection. DecouplingcapacitorinputforreferenceofchannelpairC. REFCP 63 AI ConnecttothedecouplingcapacitoraccordingtothePowerSupplyRecommendationssection. DecouplingcapacitorinputforreferenceofchannelpairD. REFDN 3 AI ConnecttothedecouplingcapacitorandAGNDaccordingtothePowerSupplyRecommendationssection. DecouplingcapacitorinputforthechannelpairDreference. REFDP 6 AI ConnecttothedecouplingcapacitoraccordingtothePowerSupplyRecommendationssection. Hardwaremode(HW/SW=0):internal referenceenableinput. Hardwaremode(HW/SW=0):internalreferenceenableinput. Whenhigh,theinternalreferenceisenabled Whenhigh,theinternalreferenceisenabled(thereferencebuffers (thereferencebuffersarealsoenabled). arealsoenabled). Whenlow,theinternalreferenceisdisabled Whenlow,theinternalreferenceisdisabledandanexternal REFEN/WR 11 DI/DI andanexternalreferenceisappliedat referenceisappliedatREFIO. REFIO. Softwaremode(HW/SW=1):writeinput. TheparalleldatainputisenabledwhenCS Softwaremode(HW/SW=1):connecttoDGNDorDVDD.The andWRarelow.Theinternalreferenceis internalreferenceisenabledbyCONFIGbitC15(REFEN). enabledbyCONFIGbitC15(REFEN). Referencevoltageinput/output. TheinternalreferenceisenabledbytheREFEN/WRpininhardwaremodeorbyCONFIGbitC15(REFEN)in REFIO 56 AIO softwaremode.Theoutputvalueiscontrolledbytheinternaldigital-to-analogconverter(DAC),CONFIGbits C[9:0].ConnecttoadecouplingcapacitoraccordingtothePowerSupplyRecommendationssection. Negativereferenceinput/outputpin. REFN 55 AI ConnecttoadecouplingcapacitorandAGNDaccordingtothePowerSupplyRecommendationssection. Resetinput,activehigh. RESET 10 DI ThispinabortsanyongoingconversionsandresetstheinternalConfigurationregister(CONFIG)to000003FFh. Avalidresetpulsemustbeatleast50nslong. Hardwaremode(HW/SW=0):standbymodeinput. Whenlow,theentiredeviceispowereddown(includingtheinternalconversionclocksourceandreference). STBY 9 DI Whenhigh,thedeviceoperatesinnormalmode. Softwaremode(HW/SW=1):connecttoDGNDorDVDD. ThestandbymodecanbeactivatedusingCONFIGbitC25(STBY). 8 Copyright©2011–2016,TexasInstrumentsIncorporated ADS8528,ADS8548,ADS8568 www.ti.com.cn ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 7 Specifications 7.1 Absolute Maximum Ratings overoperatingfree-airtemperaturerange(unlessotherwisenoted)(1) MIN MAX UNIT HVDDtoAGND –0.3 18 HVSStoAGND –18 0.3 Supplyvoltage V AVDDtoAGND –0.3 6 DVDDtoDGND –0.3 6 Analoginputvoltage HVSS–0.3 HVDD+0.3 V ReferenceinputvoltagewithrespecttoAGND AGND–0.3 AVDD+0.3 V DigitalinputvoltagewithrespecttoDGND DGND–0.3 DVDD+0.3 V GroundvoltagedifferenceAGNDtoDGND ±0.3 V Inputcurrenttoallpinsexceptsupply ±10 mA Maximumvirtualjunctiontemperature,T 150 °C J Storagetemperature,T –65 150 °C stg (1) StressesbeyondthoselistedunderAbsoluteMaximumRatingsmaycausepermanentdamagetothedevice.Thesearestressratings only,whichdonotimplyfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderRecommended OperatingConditions.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. 7.2 ESD Ratings VALUE UNIT Human-bodymodel(HBM),perANSI/ESDA/JEDECJS-001(1) ±2500 V Electrostaticdischarge V (ESD) Charged-devicemodel(CDM),perJEDECspecificationJESD22-C101(2) ±500 (1) JEDECdocumentJEP155statesthat500-VHBMallowssafemanufacturingwithastandardESDcontrolprocess. (2) JEDECdocumentJEP157statesthat250-VCDMallowssafemanufacturingwithastandardESDcontrolprocess. 7.3 Recommended Operating Conditions overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN NOM MAX UNIT AVDD Analogsupplyvoltage 4.5 5.0 5.5 V DVDD BufferI/Osupplyvoltage 2.7 3.3 5.5 V HVDD Inputpositivesupplyvoltage 5.0 15.0 16.5 V HVSS Inputnegativesupplyvoltage –16.5 –15.0 –5.0 V T Operatingambienttemperaturerange –40 25 125 °C A 7.4 Thermal Information ADS85x8 THERMALMETRIC(1) RGC(VQFN) PM(LQFP) UNIT 64PINS 64PINS R Junction-to-ambientthermalresistance 22 48.5 °C/W θJA R Junction-to-case(top)thermalresistance 9.0 9.4 °C/W θJC(top) R Junction-to-boardthermalresistance 3.6 21.9 °C/W θJB ψ Junction-to-topcharacterizationparameter 0.1 0.3 °C/W JT ψ Junction-to-boardcharacterizationparameter 2.9 21.4 °C/W JB R Junction-to-case(bottom)thermalresistance 0.3 n/a °C/W θJC(bot) (1) Formoreinformationabouttraditionalandnewthermalmetrics,seetheSemiconductorandICPackageThermalMetricsapplication report,SPRA953. Copyright©2011–2016,TexasInstrumentsIncorporated 9 ADS8528,ADS8548,ADS8568 ZHCS163C–AUGUST2011–REVISEDFEBRUARY2016 www.ti.com.cn 7.5 Electrical Characteristics: General AllminimumandmaximumspecificationsareatT =–40°Cto+125°C,specifiedsupplyvoltagerange,VREF=2.5V A (internal),V =±10V,andf =max,unlessotherwisenoted.TypicalvaluesareatT =25°C,HVDD=15V,HVSS= IN DATA A –15V,AVDD=5V,andDVDD=3.3V. PARAMETER TESTCONDITIONS MIN TYP MAX UNIT ANALOGINPUT RANGEpin,RANGEbit=0 –4VREF 4VREF CHXX Bipolarfull-scalerange V RANGEpin,RANGEbit=1 –2VREF 2VREF Inputrange=±4VREF 10 Inputcapacitance pF Inputrange=±2VREF 20 Inputleakagecurrent Noongoingconversion –1 1 μA Aperturedelay 5 ns Aperturedelaymatching CommonCONVSTforallchannels 100 ps Aperturejitter 50 ps PSRR Power-supplyrejectionratio AtoutputcodeFFFFh,relatedtoHVDDandHVSS –78 dB REFERENCEVOLTAGEOUTPUT(REFOUT) 2.5-Voperation,REFDAC=3FFh 2.485 2.5 2.515 2.5-Voperation,REFDAC=3FFhat25°C 2.496 2.5 2.504 VREF Referencevoltage V 3.0-Voperation,REFDAC=3FFh 2.985 3.0 3.015 3.0-Voperation,REFDAC=3FFhat25°C 2.995 3.0 3.005 dVREF/dT Referencevoltagedrift ±10 ppm/°C PSRR Power-supplyrejectionratio AtoutputcodeFFFFh,relatedtoAVDD –77 dB IREFOUT Outputcurrent Atdccurrent –2 2 mA IREFSC Short-circuitcurrent(1) 50 mA tREFON Turn-onsettlingtime 10 ms AtREF_xP,REF_xNpins 4.7 10 μF Externalloadcapacitance AtREFIOpin 100 470 nF REFDAC Tuningrange Internalreferenceoutputvoltagerange 0.2VREF VREF V REFDACresolution 10 Bits DNLDAC REFDACdifferentialnonlinearity –1 ±0.1 1 LSB INLDAC REFDACintegralnonlinearity –2 ±0.1 2 LSB VOSDAC REFDACoffseterror VREF=0.5V(DAC=0CDh) –4 ±0.65 4 LSB REFERENCEVOLTAGEINPUT(REFIN) VREFIN Referenceinputvoltage 0.5 2.5 3.025 V Inputresistance 100 MΩ Inputcapacitance 5 pF Referenceinputcurrent 1 μA DIGITALINPUTS(2)(CMOSwithSchmitt-TriggerLogicFamily) DVDD+ High-levelinputvoltage 0.7DVDD V 0.3 DGND– Low-levelinputvoltage 0.3DVDD V 0.3 Inputcurrent VI=DVDDtoDGND –50 50 nA Inputcapacitance 5 pF DIGITALOUTPUTS(2) Outputcapacitance 5 pF Loadcapacitance 30 pF High-impedance-stateoutputcurrent –50 50 nA Logicfamily CMOS DVDD– VOH High-leveloutputvoltage IOH=100μA 0.6 V DGND+ VOL Low-leveloutputvoltage IOH=–100μA 0.4 V (1) Referenceoutputcurrentisnotlimitedinternally. (2) Specifiedbydesign. 10 Copyright©2011–2016,TexasInstrumentsIncorporated

Description: